# Towards the Pervasive Formal Verification of Multi-Core Operating Systems and Hypervisors Implemented in C

Dissertation zur Erlangung des Grades des Doktors der Ingenieurswissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultäten der Universität des Saarlandes

vorgelegt von

# **Sabine Bettina Schmaltz**

Saarbrücken, Dezember 2012

Institut für Rechnerarchitektur und Parallelrechner, Universität des Saarlandes, 66041 Saarbrücken Hiermit erkläre ich, dass ich die vorliegende Arbeit ohne unzulässige Hilfe Dritter und ohne Benutzung anderer als der angegebenen Hilfsmittel angefertigt habe. Die aus anderen Quellen oder indirekt übernommenen Daten und Konzepte sind unter Angabe der Quelle gekennzeichnet. Die Arbeit wurde bisher weder im In- noch im Ausland in gleicher oder ähnlicher Form in anderen Prüfungsverfahren vorgelegt.

Saarbrücken, im Dezember 2012

| Tag des Kolloquiums      | 10. Mai 2013                                           |

|--------------------------|--------------------------------------------------------|

| Dekan                    | Prof. Dr. Mark Groves                                  |

| Prüfungsausschuss        |                                                        |

| Vorsitz                  | Prof. Dr. Reinhard Wilhelm, Universität des Saarlandes |

| 1. Gutachter             | Prof. Dr. Wolfgang J. Paul, Universität des Saarlandes |

| 2. Gutachter             | Prof. Dr. Kurt Mehlhorn, Universität des Saarlandes    |

| Akademischer Mitarbeiter | Dr. Mikhail Kovalev, Universität des Saarlandes        |

Copyright © by Sabine Schmaltz 2012. All rights reserved. No part of this work may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photography, recording, or any information storage or retrieval system, without permission in writing from the author. An explicit permission is given to Saarland University to reproduce up to 100 copies of this work and to publish it online. The author confirms that the electronic version is equal to the printed version. It is currently available at

http://www-wjp.cs.uni-saarland.de/publikationen/Schmaltz12.pdf.

# Abstract

#### Short Abstract

This thesis deals with a semantic model stack for verification of functional correctness of multicore hypervisors or operating systems. In contrast to implementations based on single-core architectures, there are additional features and resulting challenges for verifying correctness properties in the multi-core case, e.g. weak memory models (store buffers), or an inter processor interrupt mechanism.

The Verisoft XT project had the goal of verifying correctness of the Microsoft Hyper-V hypervisor and achieved great code verification results using the concurrent C verification tool VCC developed by our project partners during the project. A sound mathematical theory to support code verification was not established.

To remedy this shortcoming, we sketch a model stack for a simplified multi-core architecture based on a simplified MIPS model for system programmers and illustrate on a high level of abstraction how to obtain a simulation between neighboring models. A hardware model for this architecture is formalized at a detailed level of abstraction of the model stack. In addition, this thesis provides operational semantics for a quite simple intermediate language for C as well as an extension of this semantics with specification (ghost) state and code which can serve as a basis for arguing the soundness of VCC. Due to the powerful nature of specification code, a simulation between annotated and original program is not trivial. Thus, we give a pencil and paper proof.

#### Kurzzusammenfassung

Diese Arbeit befasst sich mit einem semantischen Modell-Stack für die Verifikation der Korrektheit von Multi-Core Hypervisoren oder Betriebssystemen. Im Gegensatz zu auf Implementierungen auf Single-Core Architekturen stellen sich im Multi-Core Fall zusätzliche Herausforderungen für die Verifikation von Korrektheitseigenschaften, z.B. durch schwache Speichermodelle oder die Existenz eines Inter-Prozessor-Interrupt Mechanismus.

Das Verisoft XT Projekt, welches zum Ziel hatte die Korrektheit des Microsoft Hyper-V Hypervisors zu verifizieren, erreichte unter Benutzung des Verifikationstools VCC hervorragende Resultate im Bereich der Codeverifikation. Die Erstellung einer fundierten mathematischen Theorie um diese Resultate zu untermauern wurde vernachlässigt.

Um diesen Mangel zu beheben, skizzieren wir einen Modell-Stack für eine vereinfachte Multi-Core Architektur basierend auf einem vereinfachten MIPS-Modell für Systemprogrammierer und illustrieren wie eine Simulation zwischen benachbarten Modellen erreicht wird. Ein Hardwaremodell für die Architektur wird auf einer detaillierten Abstraktionsebene präsentiert. Zusätzlich enthält diese Arbeit die operationale Semantik einer Zwischensprache für C und deren Erweiterung um Spezifikationszustand und -code welche als Basis für einen Korrektheitsbeweis des Tools VCC dienen kann. Da aufgrund der mächtigen Spezifikationssprache eine Simulation zwischen annotiertem und originalem Programm nicht trivial ist, führen wir den Beweis auf Papier.

# Acknowledgements

I would like to thank all those people without whom it would have been impossible to write this thesis. This includes all those involved in the Hyper-V verification group of the Verisoft XT project and, in particular, those who remained and worked on our shared vision of a multi-core model stack at the chair of Prof. Paul after the project ended. We had so many useful discussions both during and after the project – the feedback on my semantic models and the collaboration in our group were invaluable to developing the models to a point that it is quite certain that they are at least adequate to the tasks we intend to use them and have used them in.

I would like to specifically thank Prof. Paul for advising this thesis, my husband for supporting me during these years, and my baby son for first providing a firm – albeit not very predictable – deadline and for being a calm and content baby which allowed me to complete this thesis during maternity leave.

Saarbrücken, December 20th, 2012

Sabine Schmaltz

# Contents

| 2 | Nota | ation  |                                                         | 5  |

|---|------|--------|---------------------------------------------------------|----|

|   | 2.1  | Fundam | nental Notation                                         | 5  |

|   | 2.2  |        | ces                                                     | 7  |

|   | 2.3  | -      | ns and Logic Operators                                  | 9  |

|   | 2.4  |        | entations of Numbers                                    | 9  |

|   |      |        | Binary Numbers and Bit-Strings                          | 10 |

|   |      |        | Arithmetics on Binary Numbers                           | 11 |

|   | 2.5  |        | of Computation                                          | 12 |

|   |      |        | Automata                                                | 12 |

|   |      |        | Reachability & Traces                                   | 14 |

|   |      | 2.5.3  | Simulation Theorems                                     | 15 |

|   | 2.6  | Semant | ics of Programming Languages                            | 16 |

|   |      | 2.6.1  | Operational Semantics                                   | 16 |

|   |      |        | Formalizing Operational Semantics as an Automaton       | 17 |

|   | 2.7  | Concur | rency                                                   | 18 |

|   |      |        |                                                         |    |

| 3 |      |        | lulti-Core Hypervisor Verification                      | 21 |

|   | 3.1  |        | ction and Overview                                      | 21 |

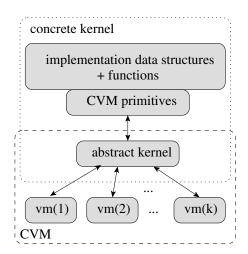

|   |      |        | Correctness of Operating System Kernels and Hypervisors | 22 |

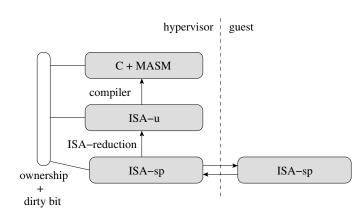

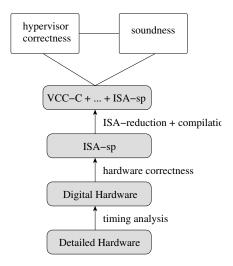

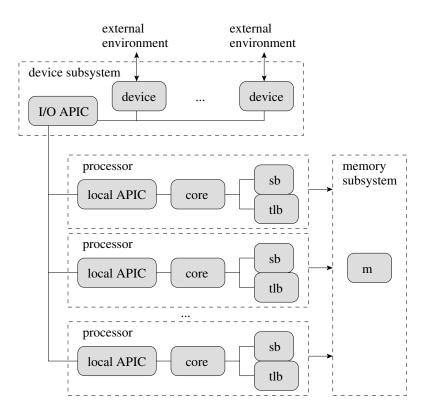

|   |      |        | Overview                                                | 23 |

|   | 3.2  | -      | ecification and Processor Correctness                   | 26 |

|   |      |        | Related Work                                            | 26 |

|   |      |        | Modeling an x86-64-like ISA-sp                          | 27 |

|   |      |        | Gate Level Correctness for Multi-Core Processors        | 28 |

|   |      |        | Future Work                                             | 29 |

|   | 3.3  |        | ting ISA-sp to ISA-u                                    | 29 |

|   |      |        | Caches                                                  | 29 |

|   |      | 3.3.2  | Store Buffers and Ownership Disciplines                 | 30 |

|   |      |        | Eliminating MMUs                                        | 31 |

|   |      | 3.3.4  | Mixed ISA-sp and ISA-u Computations                     | 32 |

|   | 2.4  |        | Future Work                                             | 32 |

|   | 3.4  |        | Language Stack                                          | 32 |

|   |      | 3.4.1  | Using Consistency Relations to Switch Between Languages | 32 |

|   |      |        | Related Work                                            | 33 |

|   |      | 3.4.3  | A Serial Language Stack for Hypervisor Verification     | 34 |

|   | 2.5  |        | Future Work                                             | 34 |

|   | 3.5  | U      | Devices                                                 | 34 |

|   |      | 3.5.1  | Related Work                                            | 35 |

1

#### Contents

|   |     | 3.5.2      | Multi-Core Processors and Devices                          | 36 |

|---|-----|------------|------------------------------------------------------------|----|

|   |     | 3.5.3      | Future Work                                                | 36 |

|   | 3.6 | Extend     | ling the Serial Language Stack to Multi-Core Computations  | 37 |

|   |     | 3.6.1      | Related Work                                               | 38 |

|   |     | 3.6.2      | Extending the Language Stack                               | 38 |

|   |     | 3.6.3      | Future Work                                                | 38 |

|   | 3.7 | Sound      | ness of VCC and its Use                                    | 39 |

|   |     | 3.7.1      | Related Work                                               | 39 |

|   |     | 3.7.2      | Soundness of VCC                                           | 39 |

|   |     | 3.7.3      | Using VCC for Languages Other Than C                       | 40 |

|   |     | 3.7.4      | Verifying Device Drivers with VCC                          | 40 |

|   |     | 3.7.5      | Future Work                                                | 41 |

|   | 3.8 | Hyper      | visor Correctness                                          | 41 |

|   |     | 3.8.1      | Related Work                                               | 42 |

|   |     | 3.8.2      | Hypervisor Verification in VCC                             | 43 |

|   |     | 3.8.3      | Future Work                                                | 43 |

|   | 3.9 | Conclu     | 1sion                                                      | 44 |

| _ |     |            |                                                            |    |

| 4 |     |            | a Formal Model of a Multi-Core MIPS Machine                | 45 |

|   | 4.1 |            | ction-Set-Architecture Overview and Tables                 | 46 |

|   |     | 4.1.1      | Instruction Layout                                         | 46 |

|   |     | 4.1.2      | Coprocessor Instructions and Special-Purpose Registers     | 47 |

|   | 4.0 | 4.1.3      |                                                            | 47 |

|   | 4.2 |            | iew of the MIPS-86-Model                                   | 51 |

|   |     | 4.2.1      | Configurations                                             | 51 |

|   | 4.0 | 4.2.2      | Transitions                                                | 53 |

|   | 4.3 |            | ry                                                         | 53 |

|   | 4.4 |            |                                                            | 54 |

|   |     | 4.4.1      | Address Translation                                        | 54 |

|   |     | 4.4.2      | TLB Configuration                                          | 56 |

|   | 4.5 | 4.4.3<br>D | TLB Definitions                                            | 56 |

|   | 4.5 |            |                                                            | 60 |

|   |     | 4.5.1      | Auxiliary Definitions for Instruction Execution            | 61 |

|   |     | 4.5.2      |                                                            | 67 |

|   |     | 4.5.3      | Auxiliary Definitions for Triggering of Interrupts         | 68 |

|   | 1.0 | 4.5.4      | Definition of Interrupt Execution                          | 69 |

|   | 4.6 |            | Buffer                                                     | 70 |

|   |     | 4.6.1      | Instruction Pipelining May Introduce a Store-Buffer        | 70 |

|   |     | 4.6.2      | Configuration                                              | 72 |

|   |     | 4.6.3      | Transitions                                                | 72 |

|   | . – | 4.6.4      | Auxiliary Definitions                                      | 72 |

|   | 4.7 | Device     |                                                            | 73 |

|   |     | 4.7.1      | Introduction to Devices, Interrupts and the APIC Mechanism | 73 |

|   |     | 4.7.2      | Configuration                                              | 74 |

|   |            | 4.7.3   | Transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75                |

|---|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|   |            | 4.7.4   | Device Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75                |

|   |            | 4.7.5   | Device Initial State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76                |

|   |            | 4.7.6   | Specifying a Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76                |

|   | 4.8        | Local A | APIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76                |

|   |            | 4.8.1   | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 77                |

|   |            | 4.8.2   | Transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79                |

|   | 4.9        | I/O API | IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80                |

|   |            | 4.9.1   | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 80                |

|   |            | 4.9.2   | Transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 81                |

|   | 4.10       | Multi-C | Core MIPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 82                |

|   |            | 4.10.1  | Inputs of the System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 83                |

|   |            | 4.10.2  | Auxiliary Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 84                |

|   |            | 4.10.3  | Transitions of the Multi-Core MIPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 85                |

|   |            | 4.10.4  | Multi-Core MIPS Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93                |

|   | 4.11       | Booting | g a MIPS-86 Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93                |

|   |            | 4.11.1  | Initial Configuration after Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 93                |

|   |            | 4.11.2  | Booting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 94                |

| 5 | ~ "        | Semant  | lies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 05                |

| 5 | 5.1        |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>95</b><br>95   |

|   | 5.1<br>5.2 |         | Programming Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 95<br>96          |

|   | 3.2        |         | eatures & Design Decisions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 90<br>98          |

|   | 5.3        |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 90<br>99          |

|   | 5.5<br>5.4 |         | Imment Parameters         Imment Second | 99<br>102         |

|   | 5.4        | • 1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 102               |

|   |            |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 102               |

|   | 5.5        |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 105               |

|   | 5.5        |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 105               |

|   |            |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107               |

|   | 5.6        | Progran | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 113               |

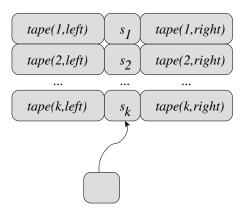

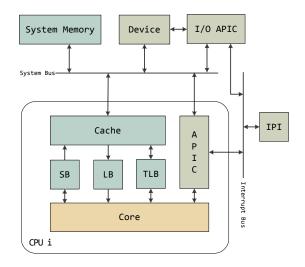

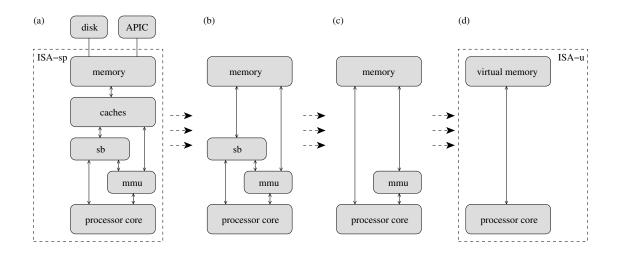

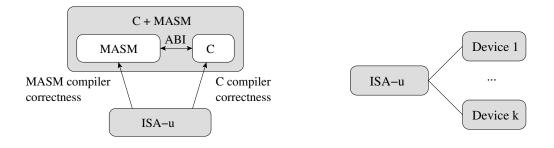

|   | 5.0        | •       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 113               |