# Diplomarbeit

# Design and Evaluation of a Superscalar RISC Processor

Mark A. Hillebrand (mah@wjpserver.cs.uni-sb.de)

Lehrstuhl Prof. Dr. W. J. Paul Fachbereich Informatik Universität des Saarlandes

April 2000

#### Eidesstattliche Erklärung

Hiermit erkläre ich an Eides Statt, daß ich die vorliegende Arbeit selbständig und ohne unerlaubte fremde Hilfe angefertigt und andere als die angegebenen Quellen und Hilfsmittel nicht benutzt habe.

Saarbrücken, den 5. April 2000

## Contents

| 1 |     | Introduction 9        |                                                |  |  |  |  |  |

|---|-----|-----------------------|------------------------------------------------|--|--|--|--|--|

|   | 1.1 | Overv                 | ••••                                           |  |  |  |  |  |

|   | 1.2 | Notes                 | on Reading                                     |  |  |  |  |  |

| 2 | Abs | stract 1              |                                                |  |  |  |  |  |

|   | 2.1 | Tomas                 | sulo Algorithm                                 |  |  |  |  |  |

|   |     | 2.1.1                 | Sequential Instruction-Stream-Based Machine    |  |  |  |  |  |

|   |     | 2.1.2                 | Tomasulo Machine                               |  |  |  |  |  |

|   |     | 2.1.3                 | Correctness                                    |  |  |  |  |  |

|   | 2.2 | Roll-E                |                                                |  |  |  |  |  |

|   |     | 2.2.1                 | Definition of Precise Roll-Back                |  |  |  |  |  |

|   |     | 2.2.2                 | Roll-Back Retirement Protocol                  |  |  |  |  |  |

|   |     | 2.2.3                 | Proof of Preciseness                           |  |  |  |  |  |

|   | 2.3 | Instru                | ction Fetch and Speculation                    |  |  |  |  |  |

|   |     | 2.3.1                 | Sequential Instruction-Memory-Based Machine 24 |  |  |  |  |  |

|   |     | 2.3.2                 | Non-Speculative Instruction Fetch              |  |  |  |  |  |

|   |     | 2.3.3                 | Speculative Instruction Fetch                  |  |  |  |  |  |

| 3 | Har | Hardware 3            |                                                |  |  |  |  |  |

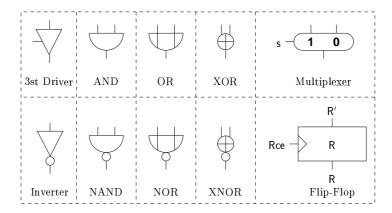

|   | 3.1 | Notati                | on                                             |  |  |  |  |  |

|   |     | 3.1.1                 | Control Signals                                |  |  |  |  |  |

|   |     | 3.1.2                 | Busses                                         |  |  |  |  |  |

|   |     | 3.1.3                 | Figures                                        |  |  |  |  |  |

|   | 3.2 | Half-U                | Jnary Number Format                            |  |  |  |  |  |

|   | 3.3 | ction Fetch Mechanism |                                                |  |  |  |  |  |

|   |     | 3.3.1                 | Overview                                       |  |  |  |  |  |

|   |     | 3.3.2                 | Algorithms                                     |  |  |  |  |  |

|   |     | 3.3.3                 | Control                                        |  |  |  |  |  |

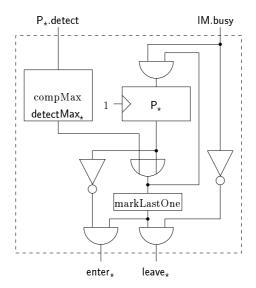

|   | 3.4 | Instru                | ction Memory Environment                       |  |  |  |  |  |

|   | 3.5 | Instru                | ction Fetch Queue Environment                  |  |  |  |  |  |

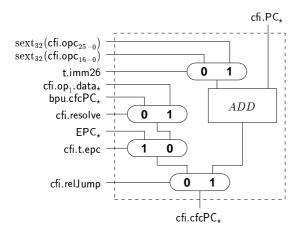

|   | 3.6 | PC en                 | vironment                                      |  |  |  |  |  |

|   | 3.7 | Predic                | etion Environment                              |  |  |  |  |  |

|   |     | 3.7.1                 | Finding the first CFI                          |  |  |  |  |  |

|   |     | 3.7.2                 | Prediction                                     |  |  |  |  |  |

|   |     | 3.7.3                 | Resolving                                      |  |  |  |  |  |

|   |     | 3.7.4                 | Construction of the CFI bus                    |  |  |  |  |  |

|   | 3.8 | Instru                | ction Window Environment                       |  |  |  |  |  |

|   |     | 3.8.1                 | Construction of the Instruction Window 49      |  |  |  |  |  |

|   |     | 3.8.2                 | Draining and Switching the Issuing IFQ 50      |  |  |  |  |  |

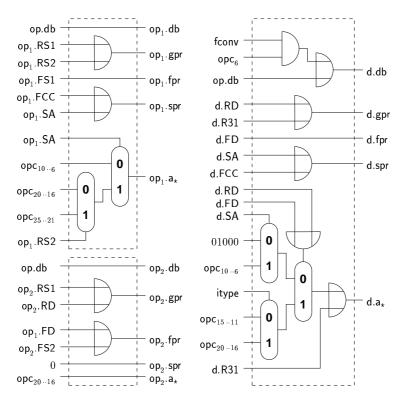

|   | 3.9 | Decod                 | e / Issue Environment                          |  |  |  |  |  |

|   |     | 3.9.1                 | Decoding the Instruction                       |  |  |  |  |  |

|   |     | 392                   | Issuing the Instruction 52                     |  |  |  |  |  |

6 CONTENTS

| ٨ | DIX                                  | Instruction Set Architect                                   | 1170                        |     |   |     | 1   | 13        |

|---|--------------------------------------|-------------------------------------------------------------|-----------------------------|-----|---|-----|-----|-----------|

| 6 | Pers                                 | spective                                                    |                             |     |   |     | 1   | 11        |

|   |                                      | 5.4.3 Register-Based Implem                                 | nentation                   | • • |   | • • | . 1 | .06       |

|   |                                      | <del>-</del>                                                | rface and Equivalence Crite |     |   |     |     | .06<br>06 |

|   |                                      |                                                             | act Multiported Queue       |     |   |     |     | 05        |

|   | 5.4                                  | Reservation Station Queue                                   |                             |     |   |     |     | 05        |

|   | E 4                                  | <u>=</u>                                                    | tation                      |     |   |     |     | 03        |

|   |                                      |                                                             | nentation                   |     |   |     |     | 99        |

|   |                                      |                                                             |                             |     |   |     |     | 98        |

|   |                                      |                                                             | act Multiported Queue       |     |   |     |     | 96        |

|   | 5.3                                  | Multiported Queue                                           |                             |     |   |     |     | 96        |

|   | 5.2                                  | Multicounter                                                |                             |     |   |     | •   | 96        |

|   |                                      |                                                             | Iultiported Round-Robin Se  |     |   |     |     | 94        |

|   |                                      | 5.1.1 Abstract View on Mul                                  |                             |     |   |     |     |           |

|   |                                      | Multiported Round-Robin Sel                                 | ector                       |     |   |     |     | 93        |

| 5 | Circ                                 | uits                                                        |                             |     |   |     |     | 93        |

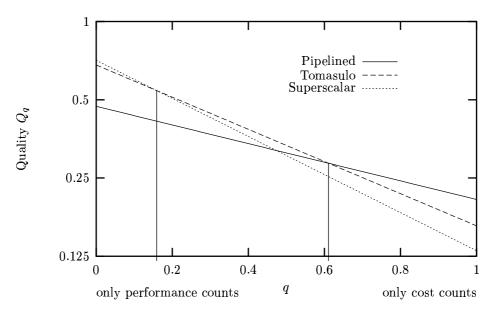

|   |                                      | 4.3.3 Quality Comparison .                                  |                             |     |   | • • | •   | 91        |

|   |                                      |                                                             |                             |     |   |     |     | 91        |

|   |                                      |                                                             | ization                     |     |   |     |     | 88        |

|   | 4.3                                  | A 2-Superscalar Processor                                   |                             |     |   |     |     | 86        |

|   | 4.2                                  | Parameter Space                                             |                             |     |   |     |     | 85        |

|   | 4.1                                  | Hardware Model                                              |                             |     |   |     |     | 85        |

| 4 | Eval                                 | luation                                                     |                             |     |   |     |     | 85        |

|   |                                      | 2 - 2.0 % Lagran + arbone recogni                           |                             | •   | • | •   | -   | ~ I       |

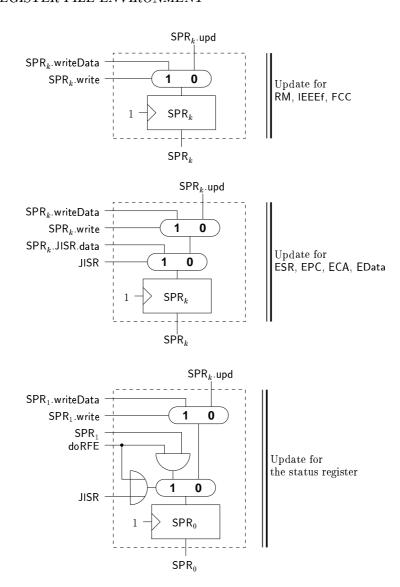

|   |                                      | 3.15.3 Special Purpose Regist                               |                             |     |   |     |     | 81        |

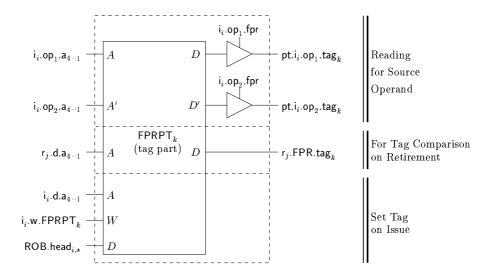

|   |                                      | 3.15.2 Floating Point Registe                               |                             |     |   |     |     | 80        |

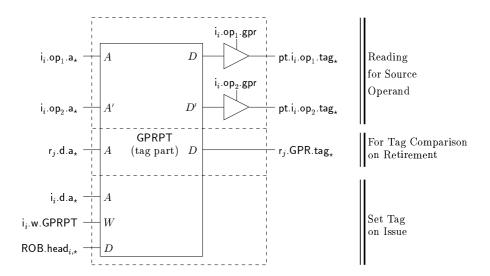

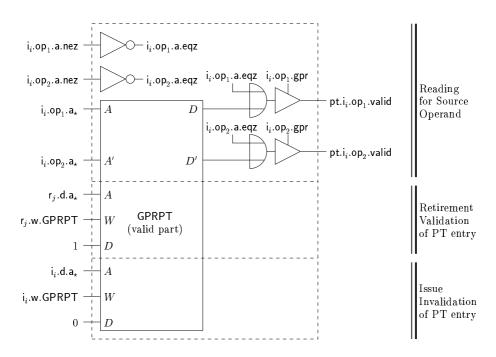

|   | 9.19                                 | 3.15.1 General Purpose Regis                                |                             |     |   |     |     | 78<br>78  |

|   | 2 1 5                                | 3.14.3 Special Purpose Regist<br>Producer Table Environment |                             |     |   |     |     | 75        |

|   |                                      | 3.14.2 Floating Point Registe                               |                             |     |   |     |     | 74        |

|   |                                      | 3.14.1 General Purpose Regis                                |                             |     |   |     |     | 74        |

|   | 3.14                                 | Register File Environment                                   |                             |     |   |     |     | 73        |

|   |                                      | 3.13.5 Retirement                                           |                             |     |   |     |     | 71        |

|   |                                      | 3.13.4 Completion                                           |                             |     |   |     |     | 71        |

|   |                                      | 3.13.3 Forwarding                                           |                             |     |   |     |     | 70        |

|   |                                      | 3.13.2 Issue                                                |                             |     |   |     |     | 70        |

|   |                                      | 3.13.1 ROB Queue Control $$ .                               |                             |     |   |     |     | 70        |

|   |                                      | Reorder Buffer Environment.                                 |                             |     |   |     |     | 68        |

|   | 3.12                                 | CDB Control Environment .                                   |                             |     |   |     |     | 68        |

|   |                                      | 3.11.5 Producer Environment                                 |                             |     |   |     |     | 67        |

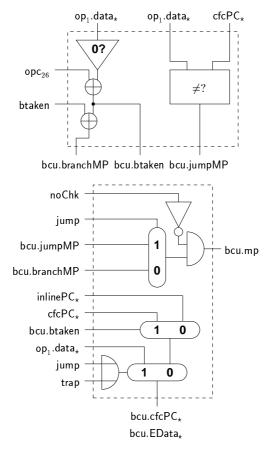

|   |                                      | 3.11.4 Branch Checker Unit .                                |                             |     |   |     |     | 65        |

|   |                                      | 3.11.3 Data Memory Function                                 |                             |     |   |     |     | 62        |

|   |                                      | 3.11.2 Floating Point Function                              |                             |     |   |     |     | 62        |

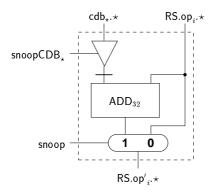

|   | 0.11                                 | 3.11.1 Arithmetical and Logic                               |                             |     |   |     |     | 61        |

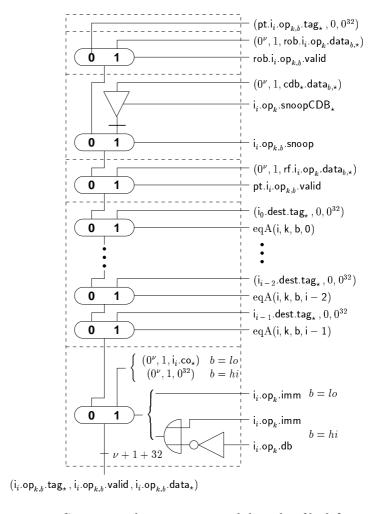

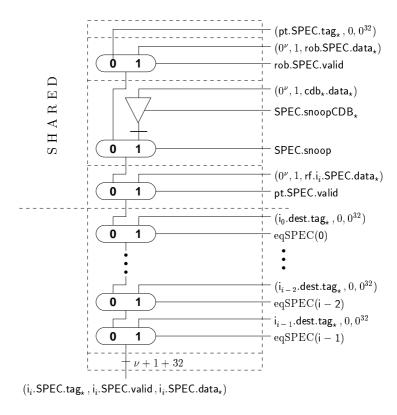

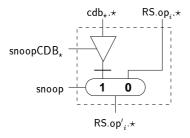

|   | 2 11                                 | 3.10.2 Snooping for source op<br>Function Unit Environments |                             |     |   |     |     | 61        |

|   |                                      |                                                             |                             |     |   |     |     | 60<br>61  |

|   | 3.10 Reservation Station Environment |                                                             |                             | 60  |   |     |     |           |

|   |                                      |                                                             |                             |     |   |     |     |           |

CONTENTS 7

| ${f B}$      | Sam | ple Branch Predictor Unit 1        | <b>17</b> |

|--------------|-----|------------------------------------|-----------|

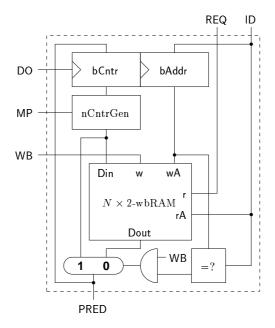

|              | B.1 | Branch Predictor                   | .17       |

|              |     | B.1.1 Implementation               | .17       |

|              |     | B.1.2 Integration in the processor | .19       |

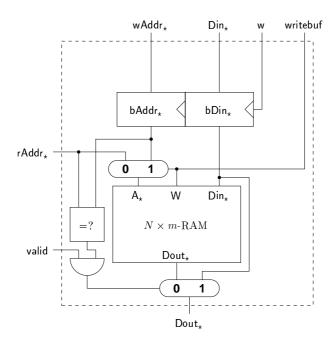

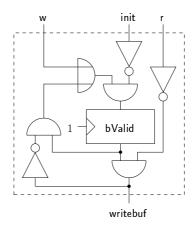

|              | B.2 | Write-Buffered RAM                 | .19       |

|              |     | B.2.1 Write                        | .19       |

|              |     | B.2.2 Read                         | 21        |

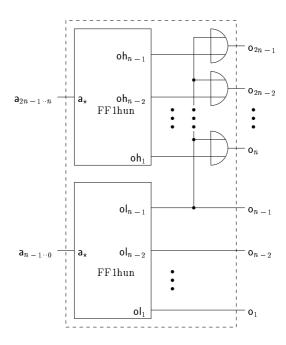

| $\mathbf{C}$ | Aux | iliary Circuits                    | 23        |

|              | C.1 | Find-First-One Half-Unary          | 23        |

|              |     | C.1.1 Definition and Construction  | 23        |

|              |     | C.1.2 Correctness                  | 23        |

|              | C.2 | Find-First- $k$ -Ones              | 23        |

|              |     | C.2.1 Definition                   | 23        |

|              |     | C.2.2 Construction                 | 24        |

|              |     | C.2.3 Correctness                  | 24        |

|              |     | C.2.4 Different Interpretation     | 24        |

|              | C.3 | Multiple Incrementer               | 25        |

8 CONTENTS

### Chapter 1

### Introduction

Processor design tries to increase the computing power of microprocessors by the advances in two fields of research. In the first, speed-up is achieved by physical advances in circuitry like reduced gate delay and an increased integration density or wafer size. In the second, refined or new algorithmic strategies are implemented decreasing the cycle-per-instruction (CPI) rate of a processor.

One approach in the second field that has been followed with considerable success is the development of superscalar processors. Such processors execute instructions in parallel while retaining the traditional sequential semantics of programs.

This thesis develops a superscalar processor on formal basis. Our superscalar processor falls into two parts: an instruction fetch mechanism and a superscalar DLX processor core implementing the Tomasulo algorithm. The instruction fetch mechanism loads instruction from the instruction memory and by sorting them in program order produces the so-called *instruction stream*. The processor takes the instruction stream and executes it as fast as possible. This combination of fetch mechanism and processor is extended by speculative execution (in the context of branch prediction) and by a precise interrupt mechanism.

#### 1.1 Overview

The remaining part of this thesis is organized in five chapters:

- Chapter 2 develops the formal framework of our processor. It contains formal approaches and proofs of correctness of a superscalar Tomasulo algorithm, a precise roll-back mechanism and a (speculative) instruction fetch mechanism.

- Chapter 3 describes the implementation of the hardware of our processor design hierarchically descending down to gate-level. The hardware model used for the description is that of [MP95]. It provides a formal background and is easily evaluated.

- Chapter 4 examines the parameter space of the proposed processor design and compares variants of it to existing processor designs from [MP95, MP00, Krö99].

- Chapter 5 defines modules used in the machine description from chapter 3. These modules represent integral functional parts of the processor. Therefore their correctness is of great importance to the correctness of the whole processor design; formal criteria for correctness are specified and proven.

• Chapter 6 draws conclusions from the presented design, the formal approach and its evaluation. It also points out the fields that may be of interest for further research.

### 1.2 Notes on Reading

We assume that the reader is familiar with the concepts of circuit and processor design as developed in [KP95, MP95, MP00]. For the understanding of a non-superscalar DLX design implementing the Tomasulo algorithm, [Krö99] is of further help.

### Chapter 2

### Abstract Model

This chapter develops an abstract model for a superscalar hardware in three steps:

- Section 2.1 presents a superscalar Tomasulo scheduling algorithm. The algorithm handles the execution of instruction streams, sequences of instructions without control flow changes. This limitation is removed later on. The correctness of the algorithm is proven.

- Section 2.2 extends the Tomasulo algorithm by a precise roll-back mechanism. A precise roll-back mechanism stops the execution of an instruction stream at a specified instruction  $I_n$ ; the instruction following  $I_n$  must not modify the state of the machine according to its sequential semantics. Precise roll-back is needed for the implementation of precise interrupts and speculative execution. The correctness of the roll-back mechanism is proven.

- Section 2.3 develops the concepts of an instruction fetch mechanism and of a speculative instruction fetch mechanism. These concepts are needed to provide the transition from instruction-stream based machines (that nobody builds) to real-life instruction-memory-based machines (with speculative execution). The speculation makes use of the precise roll-back mechanism to take back the effects of falsely executed instructions.

This chapter does not treat data memory and interrupts specifically. The exact manner of their treatment is often only defined by concrete system architectures. This is not the level of generalization we aim for in this chapter; nevertheless, in chapter 3 data memory and interrupts are treated in the environment of the DLX architecture.

### 2.1 Tomasulo Algorithm

The section describes a superscalar Tomasulo scheduling algorithm. It executes a dynamic instruction stream  $l_1, l_2, \ldots$  out-of-order while preserving the sequential semantics.

Our approach is in three steps. First, we define the semantics of an *instruction stream* by a sequential instruction-stream-based machine  $IS_{seq}$ . Second, a super-scalar Tomasulo machine TM is defined by description of the global structure and the scheduling protocols. In the third step, it is shown that TM simulates  $IS_{seq}$ . This is done by showing the data consistency theorem and the termination lemma.

#### 2.1.1 Sequential Instruction-Stream-Based Machine

We define the model of an instruction-stream-based sequential machine,  $IS_{seq}$ . The machine  $IS_{seq}$  has #reg registers  $R_1, \ldots, R_{\#reg}$  over the finite domain DOM. These registers are referenced by the indices  $\mathcal{R} := \{1, \ldots, \#reg\}$ . Instructions are executed from the *instruction stream*. In cycle n the machine executes  $I_n$ , a tuple:

$$I_n = (op, \delta, dop_1.A, \dots, dop_{\delta}.A, \sigma, sop_1.A, \dots, sop_{\sigma}.A)$$

The function op:  $DOM^{\sigma} \longrightarrow DOM^{\delta}$  computes the results of the operation;  $\delta$  is the number of destination operands and  $dop_1.A, \ldots, dop_{\delta}.A \in \mathcal{R}$  are their identifiers (pairwise distinct);  $\sigma$  is the number of source operands and  $sop_1.A, \ldots, sop_{\sigma}.A \in \mathcal{R}$  are their identifiers. With

$$(\mathsf{result}_1, \dots, \mathsf{result}_\delta) \ = \ \operatorname{op}\left(\mathsf{R}_{\mathsf{sop}_1.\mathsf{A}}, \dots, \mathsf{R}_{\mathsf{sop}_\sigma.\mathsf{A}}\right)$$

and primed registers denoting "new", i.e. next-cycle values of registers, the semantics of the instruction  $I_n$  is defined as

$$\mathsf{R'}_\mathsf{A} \ := \ \left\{ \begin{array}{ll} \mathsf{result}_1 & \mathrm{if} \ \mathsf{A} = \mathsf{dop}_1.\mathsf{A} \\ \mathsf{result}_2 & \mathrm{if} \ \mathsf{A} = \mathsf{dop}_2.\mathsf{A} \\ & \vdots & \vdots & \ddots \\ \mathsf{result}_\delta & \mathrm{if} \ \mathsf{A} = \mathsf{dop}_\delta.\mathsf{A} \\ & \mathsf{R}_\mathsf{A} & \mathrm{otherwise} \end{array} \right. .$$

Note, that a generalization on multiple, orthogonal destination operands ( $\delta > 1$ ) is not used in real machines. Usually just one general destination operand and additional fixed-addressed destination operands (like operation flags) are sufficient. However, we allow  $\delta \geq 1$  for two reasons: first, our approach to fetch mechanisms takes advantage of this fact, justifying the extra effort. Second, the simplifications used in machines having additional fixed-address destinations can be justified on the basis of algorithms for  $\delta > 1$ .

For ease notation, we consider  $\sigma$  and  $\delta$  fixed for the instruction set of the machine. A configuration of the machine stores (the values of) the registers. Instruction  $l_n$  is supposed to arrive in cycle n and is therefore not stored in the configuration.

#### 2.1.2 Tomasulo Machine

#### Informal description of the Tomasulo algorithm

This algorithm was originally published by Tomasulo in [Tom67] in the year 1967. Written first for a very specific environment, this algorithm can be easily adopted for more general architectures. The algorithm associates each instruction and its destination registers on execution with a state-unique identifier, a small natural number, called tag. On requesting a source register, an instruction either receives the (correct) value of this register, or the tag of a previous instruction computing it. On receiving a tag, the instruction has to wait until the result becomes available by a global result broadcast system. If all operands are gathered, an instruction may start execution. On completing execution, the instruction broadcasts tag and results in the whole machine for the benefit of instructions awaiting their source operands. Note that instructions awaiting execution need only to be connected to the global result broadcast system without taking up any other machine resources. A data structure, called reservation station, serves this purpose for a single instruction.

<sup>&</sup>lt;sup>1</sup>State-unique means that in each cycle there is at most one instruction in execution holding the identifier. In the machine, the tags are *recycled* if not used; so the same tag may identify different instructions in different states.

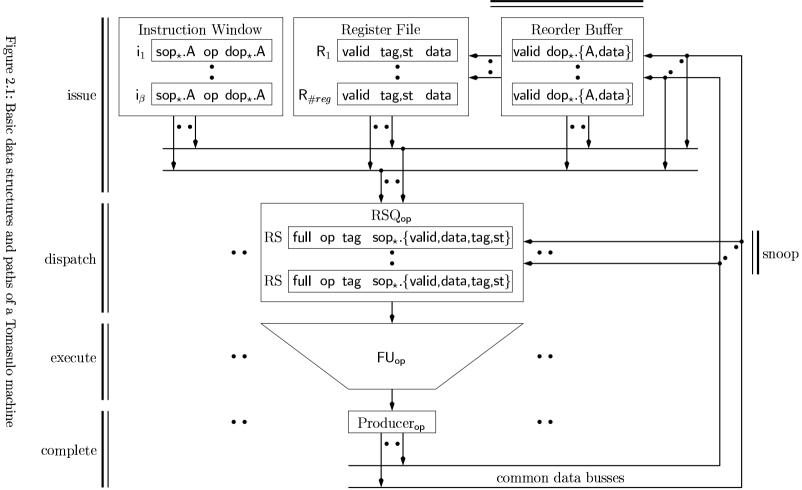

#### Basic Data Structures and Paths of a Tomasulo Machine

The figure 2.1 shows the basic data structures and paths of a superscalar Tomasulo machine. The figures are annotated with the scheduling phases of an instruction.

The following components are present in a Tomasulo machine:

- The instruction window buffers incoming instruction in slots  $i_1$  to  $i_\beta$ . Each round, the machine tries to start the execution of as many of these instructions as possible. According to the definition of the abstract machine,  $i_i$  is a tuple of source operand addresses  $i_i.sop_1$  to  $i_i.sop_\sigma$ , an operation code  $i_i.op$  and destination operand addresses  $i_i.dop_1$  to  $i_i.dop_\delta$ .

- The register file contains a tuple (valid, tag, st, data) for each register R<sub>i</sub>. Two invariants will hold for the register file:

- If  $R_i$ .valid = 1 then  $R_i$ .data contains the data of the last instruction writing to  $R_i$  up to the current machine cycle.

- If  $R_i$ .valid = 0, then  $R_i$ .tag holds the tag of the *producing instruction*, i.e. the newest instruction having  $R_i$  as destination operand. The item  $st \in \{1, \ldots, \delta\}$  then specifies the index of the destination operand having address i.

- The common data busses are the global result broadcast system for the machine. Each common data bus bears a tuple  $(tag, result_1, \ldots, result_{\delta})$  of a tag and the associated results.

- The reorder buffer contains for each instruction currently in execution a record, addressed by the instruction's tag, with the following items: the items  $\mathsf{dop}_1$ . A to  $\mathsf{dop}_\delta$ . A buffer the destination addresses of the instruction. The valid flag signals 1, if the instruction has already broadcast its results on a common data bus. In this case, the items  $\mathsf{dop}_1$ . data to  $\mathsf{dop}_\delta$ . data store the results. The reorder buffer writes results back to the register file in program order.

- The reorder buffer is organized as a simple wrap-around queue. The variable ROB.head points to the head of the queue, which is also the oldest instruction. The variable ROB.tail points to the next free entry of the queue, unless ROB.tail = ROB.head which signals a full reorder buffer. The constant ROB-SIZE denotes the size of the reorder buffer.

- Reservation station queues are collections of buffers, called reservation stations, for instructions waiting for their source operands to be broadcast on the common data busses. A reservation station contains the following items: the item full indicates valid reservation station contents; the item op is an operation identifier; the tag of the instruction that the reservation holds is stored in the item tag; a tuple  $sop_{\sigma}$  for each source operand.

- The source operand tuple contains the correct operand data, if valid = 1; otherwise it holds the tag and subtag of the producing instruction.

An instruction  $i_i$  is executed from the machine in the following way. On *issue* it is taken from the instruction window, associated with a tag from which the reorder buffer can reconstruct program order and put it an appropriate reservation station. Its source operands may either contain valid data or correct tag and subtag information. The instruction will remain in the reservation station until it has gathered all its missing source operands from the common data busses in a process called snooping. Having valid source operand data, the instruction will eventually leave its reservation station and be dispatched to its functional unit for execution. The functional unit computes the result busses and passes them via an interface called producer to one of the common data busses. This step is called completion. The

retirement / writeback

reorder buffer stores the result and will write it back to the register file in *program* order, i.e. after the results of all previous instructions have been written to the register file. This phase is called retirement of an instruction.

The exact procedure of the five phases issue, dispatch, snooping, completion and retirement is defined in protocols below. Basically, these protocols can be obtained by unrolling the non-superscalar Tomasulo algorithm handling only one instruction per cycle.

#### Issue

Superscalar issuing (algorithm 1) processes the instructions in the instruction window  $i_1, \ldots, i_{\beta}$  with  $\beta \in I\!\!N$ , fixed, in a loop (l. 1) in program order. In line 2, a tag for the instruction  $i_i$  is obtained by adding index i to the tail pointer of the ROB. If the tag is not equal to the head pointer (i.e. the ROB is not full) and the appropriate reservation station queue for the instruction is not full,  $i_i$  may issue. The test of this condition is contained in line 3.

Instruction issue is divided in three phases: gathering the source operands (ll. 4–27), allocation of a free reservation station (ll. 28–31) and updates for the destination registers in the ROB and the register file (ll. 32–39).

Consider an iteration of the loop body of the source operand construction, ll. 4–27, and define S and R as in ll. 5–6. S is constructed according to five different cases:

First, S might be produced an accompanying instruction from the instruction window (ll. 7–11). This case is indicated if a destination operand's address of the previous instruction matches S.A. Naturally, the data is not available for the operand, and we only set the S.tag to the latest instruction's tag having destination S.A. The subtag denotes the index of the destination operand.

Second, the register R might be found valid in the register file (ll. 12–14). In this case we set the operand valid and take the data out of the register file.

Third, the operand might be broadcast on one of the common data busses (ll. 15–18). This is the case if the register's tag R.tag is found on one of the common data busses. The data can be taken from the result bus indicated by R.st and stored in the source operand.

Fourth, the operand's data may reside valid in the reorder buffer, waiting for its retirement (ll. 19–21). In this case, the data can be taken from ROB<sub>R.tag</sub>.data<sub>R.st</sub>.

With none of the previous cases meeting, the operand is still being computed in a functional unit and only its tag R.tag and subtag R.st is available (ll. 22–25).

The destined reservation station RS is filled with the instruction opcode, the destination tag, and the source operands (ll. 28–32). The notation of line 31 results in the assignment of all the items from all the source operands to all the reservation station source operands.

After gathering the source operands, the instruction has to update the register file and the ROB for each destination operand (ll. 32–39). Each destination register is invalidated, the tag information is set to the instruction's tag, the subtag information is set to the destination's index. The addresses of the destination register are stored in the ROB for further use.

In hardware, this protocol is parallelized to handle all the instructions in the instruction window simultaneously. Note the construction in lines 41-43 to stop issuing at the first instruction encountering a full reorder buffer or a non-available reservation station. On termination of the issue protocol, #issued contains the number of issued instructions.

For notation we define #issued as the value of #issued in cycle t. The same

```

1: for i \leftarrow 1 to \beta do

i_i.tag \leftarrow (ROB.tail + i) \mod ROBSIZE

if i_i.valid \land (i_i.tag \neq ROB.head) \land \overline{RSQ_{i_i.op}.full} then

3:

for all \sigma' \in \{1, \ldots, \sigma\} do

(obtain source operands)

4:

Let S denote i_i \cdot sop_{\sigma'}

5:

Let R denote R_{S.A}

6:

if \exists i^- < i : \exists \delta' \in \{1, \dots, \delta\} : i_{i^-}.dop_{\delta'}.A = S.A then

(case: window)

7:

Let i^- be maximal with \exists \delta' \in \{1, \ldots, \delta\} : i_{i^-}.\mathsf{dop}_{\delta'}.\mathsf{A} = \mathsf{S}.\mathsf{A}

8:

S.valid \leftarrow 0

9:

\mathsf{S.tag} \leftarrow \mathsf{i}_{i^-}.\mathsf{tag}

10:

\mathsf{S.st} \leftarrow \delta'

11:

else if R.valid then

12:

(case: register)

\mathsf{S.valid} \leftarrow 1

13:

\mathsf{S.data} \leftarrow \mathsf{R.data}

14:

else if \exists k : CDB_k.tag = R.tag then

(case: snoop)

15:

Let k satisfy CDB_k.tag = R.tag

16:

S.valid \leftarrow 1

17:

\mathsf{S.data} \leftarrow \mathsf{CDB}_k.\mathsf{data}_{\mathsf{R.st}}

18:

else if ROB_{R.tag}.valid then

(case: forwarding)

19:

20:

S.valid \leftarrow 1

S.data \leftarrow ROB_{R.tag}.data_{R.st}

21:

(case: tag)

22:

else

S.valid \leftarrow 0

23:

S.tag \leftarrow R.tag

24:

\mathsf{S.st} \leftarrow \mathsf{R.st}

25

end if

26:

27:

end for

Let RS denote an empty reservation station in RSQ_{i_i.op}

28:

\mathsf{RS}.\mathsf{full}' \leftarrow 1

29:

30:

RS.tag' \leftarrow i_i.tag

RS.sop'_{\star}.\star \leftarrow i_{i}.sop_{\star}.\star

31:

\mathsf{ROB}_{\mathsf{i}_\mathsf{i}.\mathsf{valid}}.\mathsf{valid} \leftarrow 0

32:

for all \delta' \in \{1, \ldots, \delta\} do

(update ROB, RF)

33:

Let D denote i_i \cdot dop_{\delta'}

34:

R_{D.A}.valid' \leftarrow 0

35:

R_{\mathrm{D.A}}.tag' \leftarrow i_i.tag

36:

\mathsf{R}_{\mathrm{D.A.st'}} \leftarrow \delta'

37:

38:

ROB_{i_1,tag}.dop_{\delta'}.A' \leftarrow D.A

end for

39:

i \leftarrow i + 1

40:

else

(could not issue i-th instruction)

41:

42:

i \leftarrow i - 1

Break out of loop, stop issuing

43:

end if

44:

45: end for

46: ROB.tail' \leftarrow (ROB.tail + i) mod ROBSIZE

47: #issued \leftarrow i

```

Algorithm 1: Superscalar issue protocol

```

1: for all reservation stations RS do

for all \sigma' \in \{1, \ldots, \sigma\} do

2:

Let S denote RS.sop_{\sigma'}

3:

if \overline{\mathsf{S.valid}} \land \exists \ k : \mathsf{CDB_k.tag} = \mathsf{S.tag} \ \mathbf{then}

(snoop S on CDB<sub>k</sub>)

4:

Let k satisfy CDB_k.tag = S.tag

5:

S.valid' \leftarrow 1

6:

S.data' \leftarrow CDB_k.data_{S.st}

7:

end if

8:

9:

end for

10: end for

```

Algorithm 2: Superscalar common data bus snooping

```

1: for all functional units FU<sub>op</sub> do

if \overline{\mathsf{FU}_{\mathrm{op}}}.\mathsf{stall} \land \exists \ j : \mathsf{RS}_{\mathsf{j}}.\mathsf{full} \land \forall \ \sigma' : \mathsf{RS}_{\mathrm{op},\mathsf{j}}.\mathsf{sop}_{\sigma'}.\mathsf{valid} = 1 \ \mathbf{then}

2:

RS \leftarrow RS_{op,j} with j fairly selected

3:

FU_{op}.op' \leftarrow RS.op

4:

FU_{op}.tag' \leftarrow RS.tag

5:

for all \sigma' \in \{1, \dots, \sigma\} do

6:

(copy source operands into FU<sub>op</sub>)

\mathsf{FU}_{\mathsf{op}}.\mathsf{sop'}_{\sigma'} \leftarrow \mathsf{RS}.\mathsf{sop}_{\sigma'}

7:

end for

8:

RS.full' \leftarrow 0

9:

end if

10:

11: end for

```

Algorithm 3: Superscalar dispatch

notation defines

$$\mathcal{IW}^t = (i_1^t, \dots, i_{\beta}^t)$$

as the instruction window presented to the machine in cycle t. The base b of this instruction window is the index of the first instruction in the window. Naturally the base can be computed by  $b = 1 + \sum_{1 \le t' \le t} \# \text{issued}^{t'}$  and we have

$$(\mathsf{i}_1^t, \dots, \mathsf{i}_\beta^t) = (\mathsf{I}_\mathsf{b}, \dots, \mathsf{I}_\mathsf{b+\beta-1})$$

#### Common Data Bus Snooping

Algorithm 2 defines the superscalar common data bus snooping protocol. The reservation stations snoop on the common data busses to gather their missing source operands' data. I.e., if a reservation station has a non-valid operand and the operand's tag is seen on a CDB (l. 4), then the data is taken from the result bus denoted by the subtag from this CDB and the operand is validated (ll. 5–7). While scanning multiple CDBs at once for an operand's tag, at most one matching CDB may be found because of uniqueness of tags in a single state.

#### Dispatch

Algorithm 3 shows the superscalar dispatch protocol. Dispatch of a full reservation station to the appropriate functional unit takes place, if all source operands are valid (l. 2). Fair candidate selection (for example by the age of the entries) is needed to ensure termination of instructions in a finite amount of time (l. 3). The reservation copies its operation code, tag and the source operands in the appropriate functional

```

1: for all functional units \mathsf{FU}_{op} do

if \mathsf{FU}_{op} has result and got \mathsf{CDB}_k-acknowledgement for next cycle then

Let T denote FU_{op}.tag

3:

\mathsf{ROB}_{\mathrm{T}}.\mathsf{valid}' \leftarrow 1

4:

CDB_k.tag' \leftarrow T

5:

for all \delta' \in \{1, \ldots, \delta\} do

6:

\mathsf{CDB_k}.\mathsf{data}_{\delta'} \leftarrow \mathsf{FU_{op}}.\mathsf{result}_{\delta'}

7:

\mathsf{ROB}.\mathsf{dop}_{\delta'}.\mathsf{data}' \leftarrow \mathsf{FU}_{\mathrm{op}}.\mathsf{result}_{\delta'}

8:

end for

10:

end if

11: end for

```

Algorithm 4: Superscalar completion protocol

Require: register file updates have lower priority than from issue protocol

```

1: for i \leftarrow 1 to \epsilon do

r_i.tag \leftarrow (ROB.head + i) \mod ROBSIZE

3:

Let r_i denote ROB_{r_i,tag}

if (r_i.tag \neq ROB.tail) \land r_i.valid then

4:

for all \delta' \in \{1, \ldots, \delta\} do

(update RF)

5:

Let A denote r_i \cdot dop_{\delta'}. A

6:

R_A.data' \leftarrow r_i.dop_{\delta'}.data

7:

if r_i.tag = R_A.tag then

(validate register on tag equality)

8:

R_A.valid' \leftarrow 1

9:

end if

10:

end for

11:

(no valid instructions left for retirement)

12:

13:

i \leftarrow i - 1

Break out of loop, stop retiring.

14:

end if

15:

16: end for

17: ROB.head' \leftarrow (ROB.head + i) mod ROBSIZE

18: #retired \leftarrow i

```

Algorithm 5: Superscalar retirement

unit (ll. 4–8). After dispatch has taken place, the reservation station is marked as empty (l. 9).

Note, that dispatch to duplicates of functional units is only a simple extension to the protocol.

#### Completion

The completion protocol (algorithm 4) puts instruction results on a common data bus. If a results is avaible and a CDB has been acknowledged by the CDB bus control (l. 2) the following actions are performed: The associated ROB entry is marked valid in l. 4; the CDB tag field is set in l. 5. The results of the instruction are copied on the CDB and into the ROB (ll. 6–9).

#### Retirement

During retirement, completed instructions are taken in program order out of the reorder buffer and their results are stored in the register file. Without interrupts,

the reorder buffer is not a necessity. However, reordering instructions is required for the precise roll-back mechanism developed in section 2.2.

Algorithm 5 defines the retirement protocol. It exploits the queue organization of the reorder buffer, with the ROB head pointing to the oldest instruction present in the reorder buffer. The retirement protocol is defined in phases. The i-th phase attempts to retire instruction  $r_i$  located at position ROB.head + i mod ROBSIZE in the queue.

Instruction  $r_i$  may retire, if it still is a valid queue entry  $(r_i.tag \neq ROB.tail)$  and  $r_i.valid = 1$ , i.e. the instruction has completed (l. 5).

All destination operands are written back into the register file (ll. 6–8). A tag comparison (l. 9) indicates, if the retiring instruction is still the producing instruction for register R. In this case, the register entry is validated (l. 10).

Note that the issue protocol and the retirement protocol concurrently write to the register file. These conflicts are resolved by giving the issue protocol a writing priority over the retirement protocol. The proof of correctness relies on this behaviour.

Like the issue protocol the retirement returns the number of processed instructions in a variable, #retired. Again, we define for notation #retired as the value of #retired in cycle t. The sequence

$$\mathcal{R}^t = \left( \mathsf{r}_1.\mathsf{tag}^t, \dots, \mathsf{r}_{\#\mathrm{retired}^t}.\mathsf{tag} \right)$$

denotes the tags of the retiring instructions in cycle t;  $r_i$ .tag is the tag of the instruction processed in the i-th retirement phase.

#### 2.1.3 Correctness

This section proves the correctness of the superscalar Tomasulo algorithm in two steps. In the first step, data-consistency is shown: all instructions receive the correct source operands as defined by the (sequential) semantics. In the second step the termination of the protocols is examined: instructions take only a finite amount of time to process.

At first we define for notation some partial functions:

$$\begin{array}{rcl} \operatorname{last}(A,n) &=& \max \left\{ n' < n \mid \exists \; \delta' : \mathsf{I}_{\mathbf{n'}}.\mathsf{dop}_{\delta'}.\mathsf{A} = A \right\} \\ \operatorname{st}(A,n) &=& \delta' \quad \text{with } \mathsf{I}_{\mathbf{n}}.\mathsf{dop}_{\delta'}.\mathsf{A} = A \\ \operatorname{result}(A,n) &=& \mathsf{I}_{\mathbf{n}}.\mathsf{result}_{\delta'} \quad \text{with } \delta' = \operatorname{st}(A,n) \\ \operatorname{tag}(A,n) &=& \mathsf{I}_{\mathbf{n}}.\mathsf{tag} \quad \text{if } \exists \; \delta' : \mathsf{I}_{\mathbf{n'}}.\mathsf{dop}_{\delta'}.\mathsf{A} = A \\ \operatorname{idx}(tag,t) &=& \max \left\{ n' \mid \mathsf{I}_{\mathbf{n'}}.\mathsf{tag} = tag \wedge \mathsf{I}_{\mathbf{n'}} \text{ issued in cycle } t' \leq t \right\} \end{array}$$

In words the notations read as follows: The index of the last instruction writing to  $R_A$  before instruction  $I_n$  is denoted by last(A, n). The subtag, i.e. index of destination operand, of instruction  $I_n$  writing to  $R_A$  is denoted by st(A, n). The result of an instruction's write to  $R_A$  is denoted by  $rac{result}{rass}(A, n)$ . The tag that has been given to instruction  $I_n$ —if it writes  $R_A$ —is denoted by  $rac{result}{rass}(A, n)$ . Finally,  $rac{result}{rass}(at)$  is the index  $rac{result}{rass}$  of the instruction lastly associated with the tag  $rac{result}{rass}$  in cycle  $rac{result}{rass}$ .

The notation  $C^t$  for some component C denotes the value of this component at the beginning of cycle t.

**Theorem 2.1** Have a reservation station RS with RS.full<sup>t</sup> = 1. Let n be the index of the instruction that RS holds, i.e.  $n := idx(RS.tag^t, t)$ . Then for all  $1 \le \sigma' \le \sigma \land A := |_{n.sop_{\sigma'}}.A$ :

$$\mathsf{RS.sop}_{\sigma'}.\mathsf{valid}^t = 0 \implies \mathsf{RS.sop}_{\sigma'}.\mathsf{tag}^t = \mathsf{tag}(A, \mathsf{last}(A, n))$$

$$\mathsf{RS.sop}_{\sigma'}.\mathsf{st}^t = \mathrm{st}(A, \mathrm{last}(A, n))$$

$$\mathsf{RS.sop}_{\sigma'}.\mathsf{valid}^t = 1 \implies \mathsf{RS.sop}_{\sigma'}.\mathsf{data}^t = \mathrm{result}(A, \mathrm{last}(A, n))$$

Corollary 2.2 (Data Consistency) If the functional units work correctly (and terminate), the superscalar Tomasulo algorithm is data consistent.

**Proof of Corollary 2.2.** Once an instruction becomes dispatched, all its source operands are valid. By the theorem, all source operand data fields contain the result of the last instruction writing to them. The functional unit therefore produces the correct result.

**Proof of Theorem 2.1.** We simultaneously prove the claim and the following invariant:

**Invariant 2.3** Let A be a register address and b the base of the instruction window  $\mathcal{IW}^t$  in cycle t. Then the following implications hold:

$$\begin{aligned} \mathsf{R}_{\mathsf{A}}.\mathsf{valid}^t &= 0 &\implies & \mathsf{R}_{\mathsf{A}}.\mathsf{tag}^t &= \mathsf{tag}(A,\mathsf{last}(A,b)) \\ & & \mathsf{R}_{\mathsf{A}}.\mathsf{st}^t &= \mathsf{st}(A,\mathsf{last}(A,b)) \\ \mathsf{R}_{\mathsf{A}}.\mathsf{valid}^t &= 1 &\implies & \mathsf{R}_{\mathsf{A}}.\mathsf{data}^t &= \mathsf{result}(A,\mathsf{last}(A,b)) \end{aligned}$$

The theorem is proved by induction over the cycles of the machine t. For the induction basis we have t=1. Since an initialization condition of the machine is assumed, the reservation stations are empty and the registers are valid and zero-valued; the claims of the theorem and the invariant therefore hold trivially. Now assume that t>1 and the invariant, the theorem and the corollary on data consistency hold for all t'< t. Let b be the base of  $\mathcal{IW}^t$ ,  $t^-:=t-1$  and  $b^-$  be the base of  $\mathcal{IW}^{t^-}$ .

First, the induction step for the invariant is shown. Define  $n^-$  maximal with the property  $b^- \le n^- < b \land \exists \ \delta' : \mathsf{I}_{\mathsf{n}^-}.\mathsf{dop}_{\delta'}.\mathsf{A} = A.$  The following two cases must be examined:

• There was an issuing instruction with destination register  $R_A$  in cycle  $t^-$ . This is equivalent to  $n^-$  having a defined value. Then, obviously last $(A, b) = n^-$ . In cycle  $t^-$ , the issue protocol sets

$$\begin{aligned} \mathsf{R}_{\mathsf{A}}.\mathsf{valid}^t &= 0 \\ \mathsf{R}_{\mathsf{A}}.\mathsf{tag}^t &= \mathrm{tag}\Big(A, b^- + \max\Big\{i \leq \#\mathrm{issued}^{t^-} \mid \exists \; \delta' : \mathsf{i_i}.\mathsf{dop}_{\delta'}^{\;\;t^-} = A\Big\}\Big) \\ &= \mathrm{tag}(A, n^-) \\ &= \mathrm{tag}(A, \mathrm{last}(A, b)) \\ \mathsf{R}_{\mathsf{A}}.\mathsf{st}^t &= \mathrm{st}\Big(A, b^- + \max\Big\{i \leq \#\mathrm{issued}^{t^-} \mid \exists \; \delta' : \mathsf{i_i}.\mathsf{dop}_{\delta'}^{\;\;t^-} = A\Big\}\Big) \\ &= \mathrm{st}\big(A, n^-\big) \\ &= \mathrm{st}\big(A, \mathrm{last}(A, b)\big) \end{aligned}$$

Note that in this case retiring instructions are (correctly) not taken into account, since the issue protocol has a higher write priority than the retirement protocol on the register file (cf. section 2.1.2).

• Now assume that we are not in the first case, i.e. there was no issuing instruction with destination register  $R_A$  in cycle  $t^-$ . Therefore:

$$last(A, b) = last(A, b^{-})$$

Further assume, there was a retiring instruction in cycle  $t^-$  that matched tag with  $R_A.tag^{t^-}$ ; i.e.

$$\exists i \leq \# \operatorname{retired}^{t^{-}} : r_{i}.\mathsf{tag} = \mathsf{R}_{\mathsf{A}}.\mathsf{tag}$$

There is at most one such i, because no two retiring instructions can have the same tag. The retirement protocol in cycle  $t^-$  correctly sets:

$$\begin{aligned} \mathsf{R}_{\mathsf{A}}.\mathsf{valid}^t &=& 1 \\ \mathsf{R}_{\mathsf{A}}.\mathsf{data}^t &=& \mathrm{result}(A,\mathrm{idx}(\mathsf{r}.\mathsf{tag})) \\ &=& \mathrm{result}\big(A,\mathrm{last}\big(A,b^-\big)\big) \\ &=& \mathrm{result}(A,\mathrm{last}(A,b)) \end{aligned}$$

If there was no retiring instructions matching tag with  $R_A$ .tag, the register, as well as last $(A, b^-)$  remaing unchanged and the induction assumption holds.

This shows the induction step for the invariant. For the induction step of the theorem two cases must be distinguished:

•  $\mathsf{RS.full}^{t^-} = 0$ . With the assumption of the theorem,  $\mathsf{RS.full}^t = 1$ , this means that an issue took place on the reservation station in cycle  $t^-$ .

If  $\mathsf{RS.sop}_{\sigma'}.\mathsf{valid}^t = 1$  the issue protocol has filled  $\mathsf{RS.sop}_{\sigma'}.\mathsf{data}$  from the register file, from a common data bus  $\mathsf{CDB}_k$  or from the reorder buffer. Because of the induction assumption on the invariant and on data consistency, each case results in:

$$\begin{array}{lll} \mathsf{RS.sop}_{\sigma'}.\mathsf{data} & = & \left\{ \begin{array}{l} \mathsf{CDB_k.dop}_{\delta'}.\mathsf{result} \\ \mathsf{ROB}_{\mathsf{RA}.\mathsf{tag}}.\mathsf{data} \\ \mathsf{R_A}.\mathsf{data} \end{array} \right. \\ & = & \left. \begin{array}{l} \mathsf{result}(A, \mathsf{last}(A, n)) \end{array} \right. \end{array}$$

Otherwise, assume  $\mathsf{RS.sop}_{\sigma'}.\mathsf{valid}^t = 0$ . If there is an  $n^-$ , maximal, with the property  $b^- \leq n^- < n \land \exists \ \delta' : \mathsf{l}_{\mathsf{n'}}.\mathsf{dop}_{\delta'}.\mathsf{A} = A$  the tag and the subtag were set by tag forwarding:

$$\begin{aligned} \mathsf{RS.sop}_{\delta'}.\mathsf{tag} &= \operatorname{tag} \Big( A, b^- + \max \Big\{ i \leq \# \mathrm{issued}^{t^-} \mid \exists \ \delta' : \mathsf{i_i.dop}_{\delta'}{}^{t^-} = A \Big\} \Big) \\ &= \operatorname{tag} \big( A, n^- \big) \\ &= \operatorname{tag} \big( A, \mathrm{last}(A, n) \big) \\ \mathsf{RS.sop}_{\delta'}.\mathsf{st} &= \operatorname{st} \Big( A, b^- + \max \Big\{ i \leq \# \mathrm{issued}^{t^-} \mid \exists \ \delta' : \mathsf{i_i.dop}_{\delta'}{}^{t^-} = A \Big\} \Big) \\ &= \operatorname{st} \big( A, n^- \big) \\ &= \operatorname{st} \big( A, \mathrm{last}(A, n) \big) \end{aligned}$$

If there is no defined  $n^-$ , then then tag and subtag are taken out of the register file. By the induction assumption for the invariant:

$$\begin{aligned} \mathsf{RS.sop}_{\delta'}.\mathsf{tag} &= & \mathsf{R}_{\mathsf{A}}.\mathsf{tag}^{t^-} \\ &= & \mathsf{tag} \big( \mathsf{last} \big( A, b^- \big) \big) \\ &= & \mathsf{tag} \big( A, \mathsf{last} \big( A, n \big) \big) \\ \mathsf{RS.sop}_{\delta'}.\mathsf{st} &= & \mathsf{R}_{\mathsf{A}}.\mathsf{st}^{t^-} \\ &= & \mathsf{st} \big( \mathsf{last} \big( A, b^- \big) \big) \\ &= & \mathsf{st} \big( A, \mathsf{last} \big( A, n \big) \big) \end{aligned}$$

• RS.full<sup> $t^-$ </sup> = 1. The reservation station was already full in the last cycle. If RS.sop<sub> $\sigma'$ </sub>.valid<sup> $t^-$ </sup>, source operand RS.sop<sub> $\sigma'$ </sub> did not change its value in the preceding cycle and the claim holds by induction assumption.

Otherwise, have  $\mathsf{RS.sop}_{\sigma'}.\mathsf{valid}^{t^-} = 0 \land \mathsf{RS.sop}_{\sigma'}.\mathsf{valid}^t = 1$ . This means that the reservation station snooped operand  $\mathsf{RS.sop}_{\sigma'}$  in the last cycle on, say,  $\mathsf{CDB_i}$ . By induction assumption, have

$$\begin{aligned} \mathsf{CDB_{j}.tag}^{t^{-}} &= \mathsf{RS.sop}_{\sigma'}.\mathsf{tag}^{t^{-}} \\ &= \mathsf{tag}(A, \mathsf{last}(A, n)) \end{aligned}$$

which implicates by the induction assumption on data consistency:

$$\begin{array}{lcl} \mathsf{RS.sop}_{\sigma'}.\mathsf{data}^t & = & \mathsf{CDB_{j}.result}_{\mathsf{RS.sop}_{\sigma'}.\mathsf{st}}^{t^-} \\ & = & \mathrm{result}(A, \mathrm{last}(A, n)) \end{array}$$

**Lemma 2.4 (Termination)** If CDB acknowledgements are fair and computations in functional units take up finite time, then the Tomasulo algorithm does not deadlock the machine.

**Proof.** This lemma is also proven by induction over the instructions in the instruction stream.

We show that the first instruction terminates. For the first instruction, all register file items are valid, the reorder buffer and all the reservation stations are empty. Since the first instruction is also first in the instruction window, the instruction window case does not apply. Therefore,  $l_0$  is issued to the appropriate reservation station with all operands valid according to the register case in the issue protocol. Dispatch takes place one cycle after issue. Since the functional unit takes only finite time to compute the result of the instruction and because of fair CDB acknowledgement, completion takes place. Retirement follows one cycle after completion, since  $l_0$  occupies the ROB head.

Now assume that instructions  $l_0,\ldots,l_{i-1}$  terminate. Issuing takes place if room is available in the ROB and the appropriate reservation station queue. Eventually, this is the case: according to the induction assumption  $l_0,\ldots,l_{i-1}$  terminate and especially leave the reservation stations and the ROB. Having space, the issue protocol processes  $l_i$ . The issue protocol states that each instruction looks for its source operands at all places where results can be found. If a source operand is not valid immediately, it is snooped on the common data busses. Therefore and because of fair dispatch acknowledgements, the instruction dispatches. The functional unit executing  $l_i$  only takes finite time to compute the result of the instruction. Because of fair CDB acknowledgements, the instruction is completed in finite time. Retirement also takes finite time, since by induction assumption all the previous instructions retire.

#### 2.2 Roll-Back

This section shows the implementation of a precise roll-back mechanism. A roll-back mechanism allows to suspend the execution of an instruction stream at a retiring instruction having tag  $r_i$ .tag  $\in \mathcal{R}^t$ , a non-trivial operation on pipelined or superscalar machines. If  $n:=\mathrm{idx}(r_i.\mathsf{tag},t)$ , preciseness requires that after roll-back, the instructions  $l_1,\ldots,l_n$  have been retired and the instructions  $l_{n+1},l_{n+2},\ldots$  do not have any effect (this definition reminds of the definition of precise interrupts [Mül97, SP88]; it is formulated differently below).

2.2. ROLL-BACK 23

A precise roll-back mechanism is an essential for support of precise interrupts and speculative execution. *Interrupts* force the machine to switch to the interrupt service routine's instruction stream on internal or external interrupt conditions. Preciseness of interrupts requires this switch to be made in well-defined and recoverable manner. *Speculative execution* needs to discard the instructions of a wrongly predicted instruction stream and to continue execution with the correct one.

This section proceeds in three steps. First, the formal definition of a precise roll-back for a superscalar machine is given. Second, precise roll-back support is incorporated in the retirement protocol. Third, we prove that the new protocol meets the formal requirements of a precise roll-back.

#### 2.2.1 Definition of Precise Roll-Back

The semantics of a precise roll-back are defined with the help of two invariants on the semantics of a sequential machine.

**Definition 2.5 (Sequential Configuration)** A configuration for the sequential machine  $IS_{seq}$  defined in section 2.1 is a tuple of the values of all its registers and the index n of the lastly executed instruction.

**Definition 2.6 (Projection on Sequential Configuration)** The projection of the Tomasulo machine TM after retirement phase i in cycle t is defined as

$$\operatorname{pr}_{i}\left(C_{TM}^{t}\right) = \left(\operatorname{idx}\left(\mathsf{r}_{i}.\mathsf{tag}^{\mathsf{t}},\mathsf{t}\right),\forall\ A:\mathsf{R}_{i,A}.\mathsf{data}'\right)$$

where R<sub>i.A</sub>.data' denotes the value of R<sub>A</sub>.data' after the i-th retirement phase.

**Definition 2.7** A machine having a precise roll-back mechanism must fulfil the following two invariants:

• The projection invariant states that in each retirement phase, the register file contains the correct register data values for the instruction up to the retiring instruction:

$$\forall 1 \leq i \leq \#retired^t, n := idx(r_i.tag, t) : pr_i(C_{TM}^t) = C_{seg}^n$$

• The halting invariant states that on executing a roll-back after instruction  $I_n$  in cycle t and after retirement phase i  $(n := idx(r_i.tag, t))$  must not change the projected configuration on empty instruction stream:

$$\forall \; t' > t, \mathsf{i_1.valid}^{t'} = 0 : \forall \; 1 \leq i' \leq \#retired^{t'} \quad : \quad \mathrm{pr}_{i'}\left(C_{TM}^{t'}\right) = C_{seq}^n$$

Remark 2.8 The projection invariant ensures the projected state of the machine equal to the state of the sequential machine at defined times. The halting variant implicitly ensures that the machine does not do something "nasty" while it has been told to roll-back. As can be seen below, this criterion is easily verified for the Tomasulo algorithm.

#### 2.2.2 Roll-Back Retirement Protocol

To implement a precise roll-back mechanism, the retirement protocol, algorithm 5, has to be modified. Algorithm 6 shows the extensions, which may be inserted between line 12 and line 13 of the original algorithm 5.

The method implemented in our machine is called roll-back by *flushing*. The machine simply wipes away all the information of instructions still resident in the machine by clearing all RSQs, the ROB and the computations in functional units (ll. 2–8).

We call the machine using the extended retirement protocol  $TM_{rb}$ .

- 1: if perform roll-back? then

- 2: Update as follows with priority over the other protocols:

- 3: Set RS.full'  $\leftarrow$  0 for all reservation stations

- 4: Clear all computations in all functional units FU<sub>op</sub>

- 5:  $\forall A : \mathsf{R}_{\mathsf{A}}.\mathsf{valid}' \leftarrow 1$

- 6: ROB.head'  $\leftarrow 0$

- 7: ROB.tail'  $\leftarrow 0$

- 8: Break out of loop (do not modify head)

- 9: end if

Algorithm 6: Extension to superscalar retirement to support precise roll-back

#### 2.2.3 Proof of Preciseness

**Lemma 2.9** The machine  $TM_{rb}$  satisfies the projection invariant.

We proof the projection invariant in the following form:

$$\forall \ t, 1 \leq i \leq \# \mathrm{retired}^t, n \coloneqq \mathrm{idx}(\mathsf{r_i}.\mathsf{tag}, t) \ , A \quad : \quad \mathsf{R_A}.\mathsf{data}' = \mathrm{result}(A, \mathrm{last}(A, n))$$

In words: in every retirement phase i each register's data contains the result of the last instruction writing to it.

The proof is by induction over the cycles t. Let  $1 \leq i \leq \# \text{retired}^t$ ,  $n := \text{idx}(\mathsf{r}_i.\mathsf{tag},t)$ . For t=1 there is nothing to show, since no instructions retires and  $TM_{rb}$  and  $\mathsf{IS}_{seg}$  are assumed to be initialized in the same way.

Let t > 1 and consider the claim true for any t' < t. Let A be a register address. If no instructions prior to and including the i-th retirements phase writes to  $R_A$ , the claim holds because of the induction assumption.

Otherwise,  $R_A$ .data' contains the data of the latest retirement writing to  $R_A$ . By data consistency and the queue order of the ROB, this is also the data of the last instruction writing  $R_A$ , so

$$R_A.data' = result(A, last(A, n))$$

**Lemma 2.10** The machine  $TM_{rb}$  satisfies the halting invariant.

**Proof.** This lemma is proven by taking a quick look at all the protocols. The issue protocol terminates directly on seeing  $i_1.valid = 0$  and does not change ROB.tail. The snooping protocol and the dispatch protocol only operate on full reservation stations of which there are none. The functional units have been told to stop any computations, so the completion protocols does not find a result to forward to the reorder buffer. The retirement protocol terminates directly on ROB.head = ROB.tail without changing ROB.head.

### 2.3 Instruction Fetch and Speculation

#### 2.3.1 Sequential Instruction-Memory-Based Machine

We define a sequential, instruction-memory-based machine,  $\mathrm{IM}_{seq}$ . The definition of  $\mathrm{IM}_{seq}$  is similar to the definition of  $\mathrm{IS}_{seq}$  given in section 2.1.1. The machine  $\mathrm{IM}_{seq}$  also has  $\#\mathrm{reg}\ registers\ \mathsf{R}_1,\ldots,\mathsf{R}_{\#\mathrm{reg}}$  over the finite domain DOM. Additionally, the machine has a special register, called the program counter register PC.

The  $\mathsf{PC} \in \{1,\ldots,N\} \subseteq DOM$  for some  $N \in I\!\!N$  determines the instructions that  $\mathrm{IM}_{seq}$  executes from the instruction memory  $\mathcal{I}\!\!M = (\mathsf{IM}_1,\ldots,\mathsf{IM}_N)$ . In the n-th cycle  $\mathrm{IM}_{seq}$  executes the instruction  $I_n := \mathsf{IM}_{\mathsf{PC}^n}$  with  $\mathsf{R}^n$  denoting the value of

the register R in the n-th cycle. The sequence of instructions  $I_1, I_2, \ldots$  is called the dynamic instruction stream, while the instructions  $\mathsf{IM}_i$  stored in the instruction memory are called the static instructions. The instructions  $\mathsf{IM}_i$  in the instruction memory are tuples of the following form:

$$\mathsf{IM}_{\mathsf{i}} = (\mathsf{op}, \delta, \mathsf{dop}_1.\mathsf{A}, \ldots, \mathsf{dop}_{\delta}.\mathsf{A}, \sigma, \mathsf{sop}_1.\mathsf{A}, \ldots, \mathsf{sop}_{\sigma}.\mathsf{A})$$

If the set of register identifiers is extended to  $\mathcal{R} := \{1, \dots, \#reg\} \cup \{PC\}$ , the tuples are of the same type as in the instruction-stream-based machine.

The semantics of the regular registers is identical to the instruction-stream-based machine. With

$$(\mathsf{result}_1, \dots, \mathsf{result}_\delta) \ = \ \operatorname{op}\left(\mathsf{R}_{\mathsf{sop}_1.\mathsf{A}}, \dots, \mathsf{R}_{\mathsf{sop}_\sigma.\mathsf{A}}\right)$$

the program counter is updated in the n-th cycle according to the following equations:

$$PC' := \begin{cases} \text{result}_1 & \text{if dop}_1.A = PC \\ \text{result}_2 & \text{if dop}_2.A = PC \\ \vdots & \vdots \\ \text{result}_\delta & \text{if dop}_\delta.A = PC \\ PC + 1 & \text{otherwise} \end{cases}$$

As an initialization condition, we set  $PC^1 := 1$ .

#### 2.3.2 Non-Speculative Instruction Fetch

This section develops the notion of an instruction fetch mechanism. Informally speaking, an instruction fetch mechanism is a machine that constructs the dynamic instruction stream out of the static instructions. A machine simulating  $\mathrm{IM}_{seq}$  naturally constructs the dynamic instruction stream at some time and may therefore be called an instruction fetch mechanism for  $\mathrm{IM}_{seq}$ . What we are rather interested in are simple machines providing the dynamic instruction stream for execution on a Tomasulo machine.

#### Definition

We construct the Tomasulo machine TM', an extension of TM. The following three modifications are made:

• The instruction window's entries are extended by an additional item PC containing the program counter of the associated instruction. This information can be used by the machine, whenever PC is needed as a source operand. So, an instruction window entry  $i_i$  is a tuple

$$i_i = (\mathsf{valid}, \mathsf{PC}, \mathsf{op}, \delta, \mathsf{dop}_1.\mathsf{A}, \ldots, \mathsf{dop}_\delta.\mathsf{A}, \sigma, \mathsf{sop}_1.\mathsf{A}, \ldots, \mathsf{sop}_\sigma.\mathsf{A})$$

- The issue protocol allows read access to its variable #issued.

- The retirement protocol is modified to report all write accesses to the PC to an external interface. This modification allows for simple fetch mechanism, as the results of computations of the Tomasulo machine can be used.

The necessary protocol changes are trivial and not included here for the sake of brevity.

Now an instruction fetch mechanism is a machine that correctly constructs the dynamic instruction stream for execution with our Tomasulo machine TM' and without deadlock:

- 1: **loop**

- 2: Fetch a basic block starting at fetchPC

- 3: Wait for the CFI to execute

- 4: Set fetchPC to the reported result

- 5: end loop

Algorithm 7: Generic scalar instruction fetch mechanism

**Definition 2.11 (Instruction Fetch Mechanism)** A machine IFM is called an instruction fetch mechanism for TM' if it constructs instruction windows  $\mathcal{IW}^t$  satisfying the following property:

For every n there is an index t such that the sequence of issued instruction and their PC of TM' in cooperation with IFM is a prefix of the sequence of issued instructions and their PC of  $IM_{seq}$ .

In conclusion we find the following theorem:

**Theorem 2.12** An instruction fetch mechanism IFM and TM' in cooperation simulate  $IM_{seg}$ .

#### Scalar Fetch Mechanism

We develop a simple fetch mechanism, called *scalar fetching* (cf. [Joh91]). The instructions are divided into two classes, the basic-block instructions (BBI) and the control flow instructions (CFI):

$$\mathsf{IM}_i \text{ is BBI } :\iff \forall \ 1 \leq \delta' \leq \delta : \mathsf{IM}_i.\mathsf{dop}_{\delta'} \neq \mathsf{PC}$$

$\mathsf{IM}_i \text{ is CFI } :\iff \exists \ 1 \leq \delta' \leq \delta : \mathsf{IM}_i.\mathsf{dop}_{\delta'} = \mathsf{PC}$

**Definition 2.13** Let  $i, l \in \mathbb{N}$ . The finite instruction sequence  $(\mathsf{IM}_i, \dots, \mathsf{IM}_{i+l-1})$  with

$$\mathsf{IM}_{i+l} \ \textit{is CFI} \ \land \ \forall j \in \{i, \dots, i+l-1\} : \mathsf{IM}_i \ \textit{is BBI}$$

is called the basic block starting at i with length l. If l = 0 then the basic block starting at i is said to be empty.

The following lemma contains an elementary but significant observation about the semantics of our new machine:

**Lemma 2.14** Let  $I_t = \mathsf{IM}_{\mathsf{PC}^t}$ . Let l be the length of the basic block starting at  $\mathsf{PC}$ . Then:

$$\forall l' \in \{0, \dots, l\} : I_{n+l'} = \mathsf{IM}_{\mathsf{PC}^{\mathsf{t}} + \mathsf{l'}}$$

**Proof.** BBIs inside a basic block do not modify the PC, so execution is sequential.

This way, the dynamic instruction sequence  $I = (I_0, I_1, ...)$  can be rewritten as an alternating sequence of basic blocks and CFIs:

$$I = (bb_0, cfi_0, bb_1, cfi_1, \ldots)$$

In this equation,  $bb_i$  is the basic block starting at  $PC(cfi_{i-1})$  and  $cfi_i$  is the CFI following  $bb_{i-1}$ . The basic blocks are possibly empty.

Lemma 2.14 justifies the generic scalar fetch mechanism for TM' shown in Algorithm 7. The fetch mechanism fetches a blocks of BBIs followed by a CFI in the

first step (line 2). After that it waits for the machine to execute the CFI (line 3). According to the communication protocol of the fetch mechanism and the machine, the machine notifies the fetch mechanism of the newly computed value for PC. This is used by the fetch mechanism to update its fetchPC in the third step (line 3). Traditional and especially non-superscalar fetch mechanisms are based on this algorithm.

#### 2.3.3 Speculative Instruction Fetch

Scalar instruction fetch much too slow for superscalar machines. This is due to the small average basic block length of about 5 instructions. This means, while superscalar machines intend to process many instructions in parallel, they have wait for new instructions every few cycles due to scalar instruction fetch.

Today's microprocessors have the ability to execute instructions *speculatively*. This means that for each CFI they can guess a target PC prior to its computation. The speculation must be verified in the Tomasulo machine. It verification is successful, the machine may continue execution; otherwise the machine must roll back and proceed execution on the "right" execution path.

#### Definition

We proceed the same way as for non-speculative instruction fetch. First, we define a Tomasulo machine  $TM_{spec}$  supporting speculative execution. Then we define speculative instruction fetch mechanisms for  $TM_{spec}$ .

The machine  $TM_{spec}$  is based on  $TM_{rb}$  and TM' with the following modifications:

• The instruction window's entries are extended by additional entries bbi, cfi and nPC. The boolean variable bbi indicates if the fetch mechanism "believes" the associated instruction to be a basic-block instruction. The boolean variable cfi indicates if the fetch mechanism "believes" the associated instruction to be a control flow instruction. The entry nPC indicates the alleged PC after the execution of the instruction, i.e. the source PC for the following instruction. So, an instruction window entry  $i_i$  is a tuple

$$i_i = (valid, PC, nPC, bbi, cfi, op, \delta, dop_1.A, ..., dop_{\delta}.A, \sigma, sop_1.A, ..., sop_{\sigma}.A)$$

- The issue protocol is modified to stop issuing on encountering an instruction that is not properly marked as BBI or CFI instruction. The fetch mechanism is notified of that condition. Furthermore, variable #issued is passed back to the fetch mechanism.

- The retirement protocol checks for every retiring instruction, if the speculated value of the next PC, nPC, matches the computed value of the next PC. If this is not the case, the machines notifies the fetch mechanism and performs a roll-back immediately *after* the offending instruction.

- Again, the retirement protocol is modified to report all write accesses to the PC to an external interface.

Algorithms 8 and 9 list the modifications necessary to the old algorithms 5 and 6. The remaining modifications again are considered straightforward and not listed here for the sake of brevity.

As can be seen, a speculative instruction fetch involves two levels of speculation.

```

1: if i_i.valid and i_i has missing or wrong mark in CFI / BBI field then

2: Notify fetch mechanism.

3: i \leftarrow i-1

4: Break out of loop, stop issuing

5: end if

```

Algorithm 8: Addition to the issue protocol

```

1: if \exists \delta' \in \{1, ..., \delta\} \land r_i.dop_{\delta'}.A = PC then

2: if r_i.dop_{\delta'}.result \neq ROB_B.nPC then

3: Initiate roll-back. Notify fetch mechanism.

4: else

5: Notify fetch mechanism of verification.

6: end if

7: end if

```

Algorithm 9: Addition to the retirement protocol

```

1: loop

if retirement protocol detects misspeculation then

3:

Set PC to the corrected version

Invalidate the instruction window

4:

else

5:

Fetch a basic-block

6:

Guess a target for the CFI and modify PC

7:

Annotate the instructions

8:

end if

9:

10: end loop

```

Algorithm 10: Generic speculative instruction fetch mechanism

First, the instruction fetch mechanism is allowed to speculate about the class of an instruction. This approach will not be followed in this thesis, although it is common for high performance fetch mechanism. For example, instruction fetch mechanisms might cache the class-information of instructions basicblock-wise, to avoid the decoding of instructions (cf. [Yeh93]).

Second, it speculates control flows, i.e. the irregular change of the PC.

Both speculations are verified and may cause a roll-back. In the first case, this is detected as early as in the issue phase. As the offending instruction is kept from issuing, no "real" roll-back is necessary. In the second case, the verification takes place in the retirement protocol. A misspeculation causes a roll-back taking back the effects of the instructions still in execution.

Now we define:

**Definition 2.15 (Speculative Instruction Fetch)** A machine SIFM is called an instruction fetch mechanism for  $TM_{spec}$  if it constructs instruction windows  $\mathcal{IW}^t$  so that the following property holds:

For every n there is an index t such that the sequence of retired instruction and their PC of  $TM_{spec}$  in cooperation with SIFM is a prefix of the sequence of issued instructions and their PC of  $IM_{seq}$ .

#### A Generic Speculative Instruction Fetch Mechanism

```

1: if rollback to cfcPC signalled then

Remove all instruction fetch queues

Let Q be a new queue

3:

fetchlFQ \leftarrow Q

4:

issuelFQ \leftarrow Q

fetchPC \leftarrow cfcPC

6:

7: end if

8: i \leftarrow 0

9: for i \leftarrow 1 to \alpha do

if IM<sub>fetchPC</sub> is CFI then

10:

Guess a result cfcPC for the update of the fetchPC register

11:

fetchIFQ.push ("valid CFI", PC = fetchPC, nPC = cfcPC)

12:

fetchPC \leftarrow cfcPC

13:

fetchlFQ \leftarrow new queue Q

14:

Break out of loop. Stop fetching.

15:

16:

fetchIFQ.push ("valid BBI", PC = fetchPC, nPC = fetchPC + 1)

17:

fetchPC \leftarrow fetchPC + 1

18:

end if

19:

20: end for

21: i_{\star}.\star \leftarrow issuelFQ.\star

22: issuelFQ.drain (#issued)

23: if issuelFQ.empty \land (fetchlFQ \neq issuelFQ) then

\mathsf{issuelFQ} \leftarrow \mathrm{next} \ \mathrm{IFQ}

25: end if

```

Algorithm 11: Queue-based speculative instruction fetch

Algorithm 10 shows the algorithm for a generic speculative instruction fetch mechanism. If the retirement protocol detects a misspeculation, it invalidates the instruction window and sets its internal PC to the corrected version (ll. 2–4). Otherwise it fetches a basic-block. Each basic-block ends in a CFI. The outcome the CFI is guessed and the PC is modified accordingly (ll. 6–8). The process repeats.

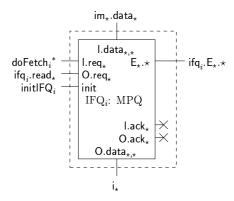

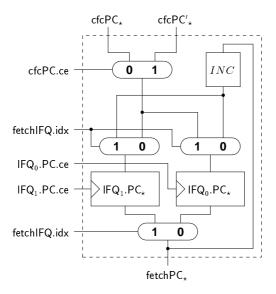

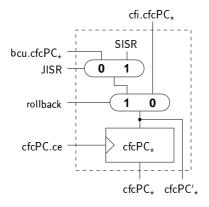

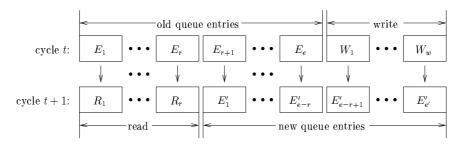

#### Queue-Based speculative instruction fetch

The generic speculative instruction is not of much use in real implementations. We present here a different algorithm closer to the implementation of chapter 3.

The algorithm maintains a list of queues, each of which will store a single basic block. The instruction fetch is decoupled from the instruction issue: it addresses the memory via the fetch PC, fetchPC, and appends instructions to a designated fetching queue until a CFI has been met. The PC computation of a CFI will be guessed and fetching continues in a new queue from the guess control flow change PC, cfcPC.

Instructions will be issued by draining them from a designated issuing IFQ. If the issuing IFQ is empty, issuing switches to the next queue.

Initialization and rollback result in the clearing of all queues and starting all over with a new queue Q, which will be fetching and issuing IFQ.

Algorithm 11 shows the algorithm just described.

### Chapter 3

### Hardware

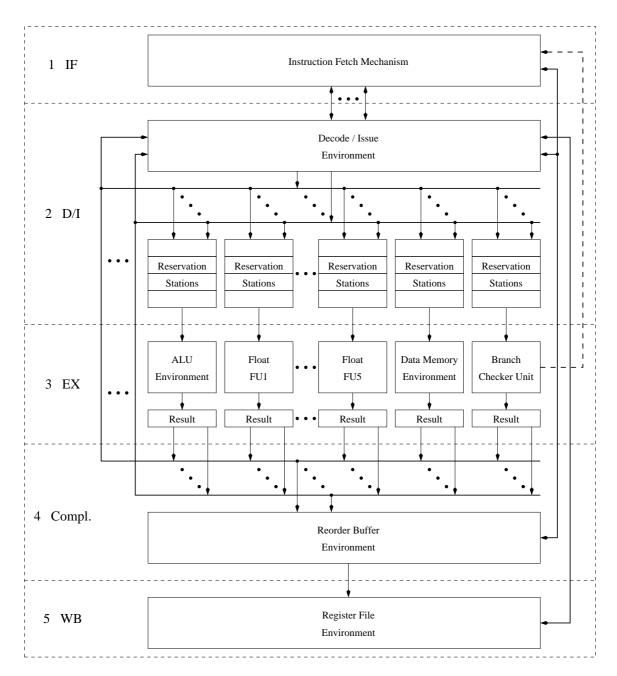

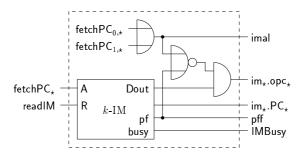

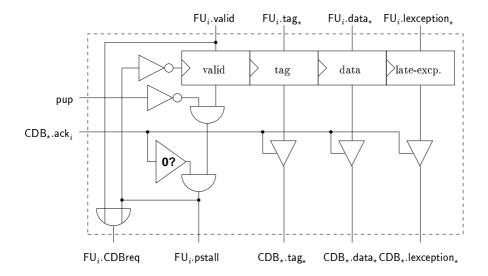

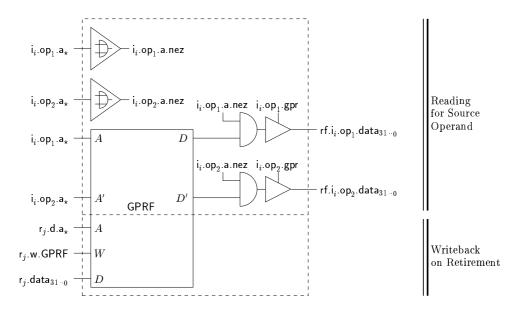

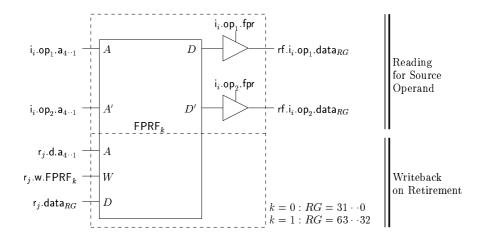

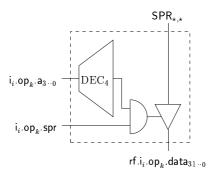

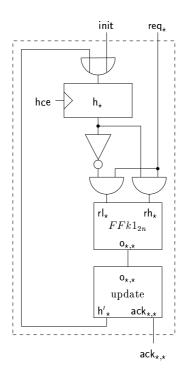

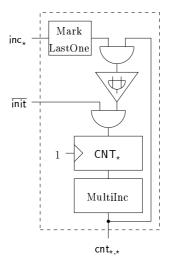

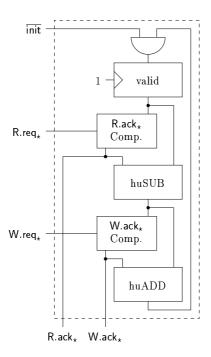

This chapter develops the hardware of a superscalar DLX processor implementing the Tomasulo algorithm. The basic structure of such a processor is in analogy to a non-superscalar version; [Krö99] develops a non-superscalar processor. Figure 3.1 on the following page shows an overview of the data paths of our processor design. The processor decomposes the execution of an instruction into five pipeline stages. In the first, the instruction fetch mechanism accesses the instruction memory, predicts control flow and puts instructions in the instruction window. From the instruction window, instructions are decoded and led on to the appropriate reservation station in the second stage. During decode and in the reservation stations the instructions gather their source operands, which may come out of the register file, the reorder buffer or from a common data bus. Instructions with available source operands are led to the third stage, the execution stage. This stage contains the functional units to compute the instruction result. The functional units may be pipelined to reduce cycle time. Computed results are put on a common data bus, in the fourth stage. The common data bus is snooped on by the reservation station as was described above, and the reorder buffer, also located in the completion stage, gathers all results in a buffer. The results leave the reorder buffer in program order to be written back in the register file in the fifth stage. The fifth stage therefore is called the write back stage.

The chapter proceeds with some notes on the notation, an introduction to a half-unary number format frequently used throughout this thesis and a detailed description of the pipeline stages.

#### 3.1 Notation

#### 3.1.1 Control Signals

Control signals are denoted by alphanumeric names set in a special font, like test  $\in \{0,1\}$ . Control signals are not limited to bit signals, they may form multi-dimensional arrays. In this case, indices are attached to the signals according to their dimension. If we have, for example, an n-bit signal bus called data, decalred in notation by  $\mathsf{data}_{\star} \in \{0,1\}^n$ , we might reference it such:

$\mathsf{data_i} \quad \text{bit } i \text{ from } \mathsf{data}$

$data_{i cdot i}$  bits j to i (in that order) from data

data\* all the bits from data

The following example demonstrates the reference to a  $m \times n$ -bit signal array / matrix called ar, declared in notation by  $\operatorname{\sf ar}_{\star,\star} \in \{0,1\}^{m \cdot n}$ . This signal array is said

Figure 3.1: Data paths of the superscalar DLX processor

3.1. NOTATION 33

to have m rows and n columns:

```

ar_{i,j} bit j from the i-th row of ar ar_{i,j\cdots k} bits j to k from the i-th row of ar ar_{i,\star} the i-th row of ar ar_{\star,j} the j-th column of ar ar_{\star,\star} all the bits from ar

```

The star notation and the range notation is also frequently used in equations. It is a shortcut notation for using an all quantifier. The following sample notational equivalences hold for  $a_*$ ,  $b_*$ ,  $c_*$ ,  $s_* \in \{0,1\}^n$  and  $o \in \{\land, \lor\}$ :

$$\begin{aligned} c_{\star} &= \mathsf{a}_{\star} &\iff & \forall \; 0 \leq n' < n : \mathsf{c}_{n'} = \mathsf{a}_{n'} \\ c_{\star} &= \overline{\mathsf{a}_{\star}} &\iff & \forall \; 0 \leq n' < n : \mathsf{c}_{n'} = \overline{\mathsf{a}_{n'}} \\ c_{\star} &= \mathsf{a}_{\star} \circ \mathsf{b}_{\star} &\iff & \forall \; 0 \leq n' < n : \mathsf{c}_{n'} = \mathsf{a}_{n'} \circ \mathsf{b}_{n'} \\ c_{\star} &= (\mathsf{s}_{\star} \; ? \; \mathsf{a}_{\star} : \; \mathsf{b}_{\star}) &\iff & \forall \; 0 \leq n' < n : (\mathsf{s}_{n'} \; ? \; \mathsf{a}_{n'} : \; \mathsf{b}_{n'}) \end{aligned}$$

Constructions like

$$c_{j \cdot \cdot i} = a_{(j+c) \cdot \cdot (i+c)}$$

$c_{\star} = test \wedge a_{\star}$

$ar_{i,\star} = a_{\star}$

are also allowed if the signals are properly typed; again, inserting an all quantifier reveals their meaning.

The standard order for writing signals is from high to low. For example, the definition  $b_{3..0} := (1, a_{3..2}, 0)$  results in

$$(b_3, b_2, b_1, b_0) := (1, a_3, a_2, 0)$$

#### 3.1.2 Busses

Often it is convenient to identify a group of signals by a single name. In our notation such signals share the same prefix ending in a dot.

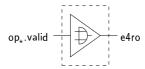

An instruction operand, for instance, might consist of a valid flag op.flag  $\in \{0,1\}$ , a data bus op.data<sub>\*</sub>  $\in \{0,1\}^{32}$  and a tag op.tag<sub>\*</sub>  $\in \{0,1\}^{5}$ . These three items form a bus, abbreviated by op.\*.

Busses themselves might also be indexed to form vectors of busses. For example, having two instruction operands denoted by  $op_1$  and  $op_2$  we might reference such:

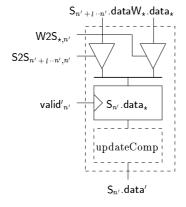

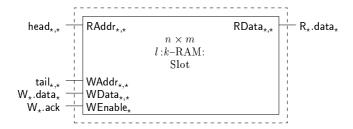

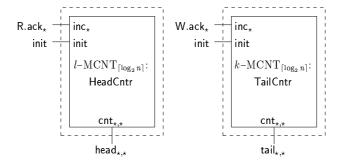

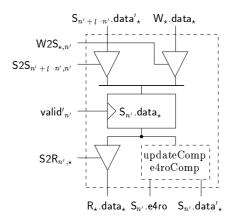

| op <sub>⋆</sub> .⋆    | both complete busses               |