# Reordering and Simulation in Concurrent Systems

Dipl.-Ing. Christoph Baumann

Institute for Computer Architecture und Parallel Computing Department of Computer Science, Saarland University

September 19, 2012

TECHNICAL REPORT

## **Abstract**

In this document we present intermediate results of our ongoing work in the field of the formal specification and verification of concurrent systems with shared memory. In particular here we focus on the specification of such systems and develop a generic framework to model their operational semantics. Every participant in the concurrent system is represented by an abstract state machine that can be instantiated individually, e.g., with instruction set architectures, device descriptions or higher-level language semantics. Machines of the system may access shared memory asynchronously and additionally communicate with each other using Moore and Mealy output signals. In order to justify the application of verification techniques on a higher level we provide a concurrent simulation theorem that allows transfering correctness properties to a lower-level specification of the overall system. The simulation theorem is based on a reordering theorem that reduces arbitrary system executions to orderly ones where we interleave machines executing blocks of steps containing at most one shared memory access. Memory safety is guaranteed by a simple ownership policy which all participants must be proven to obey.

# 1 Introduction

There is no such thing as sequentiality. In fact, as far as we can tell, the whole universe is inherently a parallel system. Galaxies, stars and planets are roaming space in parallel, steering each other by gravity and "communicating" by the emission and reflection of light. All lifeforms on Earth exist in parallel and influence each other, e.g. by producing sound waves, performing motions or applying force. On the gate level of a processor signals change their logical value in parallel and interact with each other through logic circuitry. Every electron of an atom is revolving around the atomic core in parallel with all other electrons. They are affecting each other by their electromagnetism. On any level of abstraction processes in the real world are running concurrently. Nevertheless in computer science (and possibly elsewhere) we are usually modelling this kind of concurrency in a different way.

Firstly, we look at systems in an isolated way. We encapsulate a certain number of components that make up the system we want to describe and separate it from its environment. The components can communicate with each other via shared variables or messages. Communication with the environment occurs only via defined input and output channels. Secondly, in case we do not speak about lockstep parallel systems, we interleave the steps of individual components in some arbitrary order. Thus we assume the rest of the system to pause during the step of one participant. What computer science has in common with the examples above is that systems are described at a level of detail that is appropriate to make meaningful statements about a system and to predict its behaviour.

Following these three principles seems to make it easier for the human mind to conceive the functionality of concurrent systems and to argue about them. One must however not forget that all these abstractions have prerequisites and rely on certain assumptions on lower-level properties of the system as well as the environment. For instance it is a common assumption that the environment does not interfere with the system via hidden channels. These include also physical side-channels and we assume, for instance, that bits in our system are not flipped due to electromagnetic radiation, or that the computer system running programs we are examining is not being destroyed during execution. A specification of a system is therefore only complete if one expresses also the underlying assumptions on the behaviour of its environment. Moreover the interleaving of component steps usually assumes some sequential consistent shared memory, which is not provided by default in modern computer systems. Configuring caches and address translation in a proper way and using a certain programming discipline are means to reduce caches, memory management units and store buffers. To ensure sequential consistency of the shared memory one additionally needs the absence of data races on shared variables. Memory safety conditions must guarantee that atomic updates of shared memory stay atomic until the lowest layer of specification.

In general all abstractions we make should be justified. The best justification we can have is a formal simulation proof between the abstract system and its low-level implementation. This document provides (1) a framework to model concurrent systems with shared memory and communication signals at any level of abstraction (2) a simulation theorem to relate different abstraction layers (3) a general order reduction theorem for concurrent systems that en-

ables applying the simulation theorem (4) verification conditions for memory safety (5) a complete correctness proof of our approach including the aforementioned theorems in paper and pencil mathematics.

#### 1.1 Overview

As motivated above we want to look at asynchronous concurrent systems on different layers of abstraction and connect these layers formally using simulation relations, or refinement mappings respectively. This requires defining formal semantics for every layer and we want to be able to do so in a uniform manner. To this end we introduce a framework that allows to define instances of what we call a *Concurrent System with Shared Memory and Ownership*, abbreviated by the acronym *Cosmos*. A *Cosmos* model consists essentially of a number of infinite state machines which can be instantiated individually, and a shared memory. What is special is additional specification components representing the dynamic *ownership* state.

We use a simple ownership model to keep track which memory addresses are owned by a particular machine in the system and which addresses are shared by all participating machines. We specify ownership invariants and a memory access policy based on ownership that provably guarantees memory safety if all machines adhere to it. Moreover we can use ownership later on to prove commutativity of certain machine steps. Thus it is a cornerstone principle of our approach. In fact every instantiation of a machine in the Cosmos model must come with a program logic containing individual safety conditions for operations of that machine. We require that safe operations preserve ownership invariants and perform only sound memory accesses wrt. the ownership model, i.e., they must obey the ownership policy. This policy demands, e.g., that one machine does not write addresses owned by other machines or that shared memory may only be accessed by steps that are recognized by the program logic as so-called IO steps, where IO stands for input/output. Every machine instantiation must specify which of its state transitions are considered  $\mathcal{IO}^1$ . Intuitively an  $\mathcal{IO}$  step represents a communication between machines in the *Cosmos* model and is usually implemented via shared memory.

In addition to shared memory we allow the machines also to have Moore and Mealy output signals for communication with each other as well as external inputs. These signals are useful to model interrupt lines in case of ISA models but also message protocols in case of higher-level models. Activations of internal outputs and reactions to internal inputs are considered  $\mathcal{IO}$  steps. External inputs provide an interface with the environment but also means to model nondeterminism. Thus by definition we can require all machines in a Cosmos model to be deterministic automata, and their transition functions rely only on (a portion of) the system state as well as internal and external inputs. We execute a Cosmos model consuming a sequence of external inputs and an explicit schedule determining the interleaving of machines.

Now we can have different instantiations of *Cosmos* models describing the same system at different levels of detail. For instance we might look at a computer system were C programs are executed concurrently on multiple processor cores. In the real world these programs are compiled to a certain multicore

$<sup>^1</sup>$ The individual definition of  $\mathcal{IO}$  must be however consistent with memory safety conditions

instruction set architecture (ISA) which we can also model as a Cosmos (possibly a reduced version under certain software conditions). Each program is compiled separately and there exists a local simulation relation and a theorem that links C and ISA execution on one machine. It would be desirable to compose the local simulation theorems to one global simulation theorem spanning all machines in the Cosmos. Naturally this would base on the local theorems stating that for every particular machine its local simulation relation is preserved by executions of the overall system. However we can not prove such a theorem for arbitrary interleavings of machine steps because a simulation relation need not generally hold for all states of an execution on the abstract level and usually only holds for a few steps on the concrete level where the steps are refined<sup>2</sup>. In fact we need to assume schedules on the low level where machines are executing blocks of steps from one consistency point (a configuration that is consistent to/simulates an abstract one) until the next one. Furthermore we cannot just combine arbitrary programs in a concurrent fashion. There is a number of requirements on the nature of the simulation theorems under consideration and the notion of the shared resources on both levels. We list all the necessary assumptions including memory safety on the abstract level and prove the global Cosmos model simulation theorem based on the correctness of the local simulations which have to be verified individually. The assumption of block scheduling is justified by an order reduction theorem.

In order reduction we reduce the number of possible interleavings of different processor steps. The core argument to enable reduction is that the effect of a safe concurrent system execution does only partly rely on the scheduling on machine steps. In fact it relies only on the external input sequence and the schedule of  $\mathcal{IO}$  steps. All non- $\mathcal{IO}$  actions can be reordered arbitrarily as long as program order is maintained. The reordering preserves the effect of the original trace because non- $\mathcal{IO}$  steps only modify local information. This can be enforced by the ownership policy and is the main lemma of the proof. Instead of non- $\mathcal{IO}$  operations we also speak of local steps and we call the configuration from which an  $\mathcal{IO}$  step origins  $\mathcal{IO}$  point.

For the reduction theorem we reduce arbitrary interleavings to so-called  $\mathcal{IO}$  block schedules, which are interleavings of blocks of steps of same machine. Each  $\mathcal{IO}$  block usually contains exactly one  $\mathcal{IO}$  step at the beginning of the block. We construct the blocks in a way that we are later on able to apply the local simulation theorems on them. Here we assume for simplicity that all  $\mathcal{IO}$  points are consistency points<sup>3</sup>. The reduction requires that all  $\mathcal{IO}$  block schedules are proven to obey the ownership policy and preserve ownership invariants. Then this also holds for all arbitrary schedules and for each of them we can find a consistent  $\mathcal{IO}$  block schedule. Additionally we prove that the reduction preserves safety properties. We do not consider liveness in this report. Apart from memory safety conditions the theorem also relies on certain constraints on the *Cosmos* model components and parameters that must be fulfilled by all instantiations.

The subsequent sections are structured as follows. In Section 2 we introduce the *Cosmos* model. For clarity we first develop a simplified version which

$<sup>^2</sup>$ The only exception to this is one-step simulations where one abstact step maps to a single concrete one.

$<sup>^3</sup>$ This assumption can be relaxed for more general simulations relations. A necessary precondition is that between two  $\mathcal{IO}$  points of the same machine it passes at least one consistency point.

is extended in Section 3 with additional communication channels. We procede in Section 4 to define the order reduction theorem and prove it. In Section 6 we give a semantics for a machine which only executes  $\mathcal{IO}$  blocks. In the sixth Section we first set up a framework to define local simulation theorems in a unified way. We then list the requirements needed to combine all local simulations into a global one. We conclude this report with the proof of that simulation theorem.

### 1.2 Related Work

The first formal approaches for the specification and verification of sequential programs date back to the 60s [Flo67, Hoa69]. In the subsequent decades myriads of different tools and languages have been developed to tackle the problem in a more efficient way and to apply techniques to more and complex systems. The most challenging targets for formal methods may be operating systems, and recent history has seen several attempts on the verification of sequential OS microkernels [Kle09]. The approach of the Verisoft project [AHL<sup>+</sup>09] however comes probably closest to our vision of modelling computer systems on various abstraction levels that are linked by simulation theorems, thus enabling pervasive verification. There a semantics stack was developed spanning abtraction layers from the gate level hardware description up to the user application view. Nevertheless only a sequential, academic system was considered. The succeeding Verisoft XT project aimed at transferring this approach to the real world and developed tools and methods for the formal verification of inductrial concurrent operating systems and hypervisors [CAB<sup>+</sup>09, LS09, BBBB09]. The theory presented in this report was conceived in an effort to justify the specification and verification approach used in the Verisoft XT project, were the automated verifier VCC [CDH+09] was employed to prove code correctness on the concurrent C level.

The VCC tool is just milestone in the long history of specification and verification methods for concurrent systems [Lam93]. As early as 1975 Ashcroft [Ash75] and Owicki/Gries [OG76] extended Floyd's and Hoare's methods to the concurrent case. The approach was based on assertions that were added to programs in order to show the preservation of global invariants. Instead of using programs to specify other programs Lamport suggested to use state machines and mathematical formulas as a universal specification language. His Temporal Logic of Actions (TLA) [Lam94] allows to define safety and liveness properties of programs and algorithms in a uniform and well-defined way. Systems can be composed by disjunction of TLA specifications [AL95] and specified at different levels of abstraction. In case a refinement mapping exists between two layers it can be shown that one specification implements the other by showing an implication in TLA [AL91]. However, this simulation approach seems only to be suitable for the program refinement or simple simulation theorems where the concrete specification makes steps in parallel with the abstract one (which might stutter). For general simulation theorems where n abstract steps simulate m concrete ones we can not use TLA.

In 1978 Hoare introduced an algebraic method to model communicating sequential processes [Hoa78]. Subsequently the language he proposed evolved into the well-known CSP process algebra [Hoa85] and a whole community following his his approach was formed. Several other process algebras fol-

lowed in the wake of CSP, most prominently Milner's  $\pi$ -calculus. However this methodology seems only appropriate to model systems at a very abstract level, e.g., to specify algorithms and protocols. Modelling complex systems by algebraic structures and their transformations is at best messy, if not infeasible.

Another approach to concurrent system specification are I/O Automata as introduced by Lynch and Tuttle [LT87]. I/O Automata are basically infinite state machines which are characterized by actions they can perform. Internal actions are distinguished from externally visible input and output actions that are employed for communication between automata. Lynch uses these automata to model sequential, parallel and asynchronously concurrent shared memory systems and algorithms [Lyn96]. It is possible to compose several automata into a bigger one given certain composability requirements on their actions. Moreover it was shown how to prove simulation theorems between automata. However it was not treated how the automatas working on shared variables should be composed (an overall automaton containing all subautomata was assumed) nor how simulation is maintained by composition of I/O automata. Finally the need to list all actions of an automaton and divide them into input, output and internal ones appears to be feasible for small-scale systems and algorithms. Modelling a realistic system like a modern instruction set architecture working massively on shared memory as an I/O automaton, in contrast, seems to be a rather tedious task. Nevertheless we feel that using composable state machines is the the right methodology in order to obtain a formally linked semantics stack. In this way we are inspired by the work of Lynch and Lamport. Gurevich also followed the idea of modelling systems as Abstract State Machines (ASMs) [Gur00, BG03] and a programming language exists to specify and execute such models [GRS05]. However the ASM approach does not support asynchronous concurrency [Gur04].

As to the best of our knowledge there is no prominent formalism in literature general enough to serve our purposes we define our own framework for modelling concurrent systems using well-known concepts like automata theory and simulation relations. Concerning (order) reduction a multitude of related work exists. Lipton was the first to describe how several steps of an operation could be aggregated into a monolithic atomic action, given that it contained only one access to shared memory [Lip75]. His results were improved by Doeppner [Doe77] and Lamport [LS89], who showed that safety properties are preserved by the reduction. Later Lamport [Lam90] specialized his results for systems with explicit message passing, ruling out interrupts along the way. Generally these approaches had in common that a particular program is examined and the specific operation with its sub-steps that shall be reduced is perfectly well-defined. In our case we would like to show a general reduction theorem for arbitrarily instantiated *Cosmos* models using the memory safety of all traces. In order to do so we have to reorder local steps of machines forming a schedule of IO blocks. The structure of these blocks is only constrained in that they have to start in an  $\mathcal{IO}$  block and depending on the inputs the length of a block may vary even if it starts in the same configuration. However in the approaches above one must exactly identify the consecutive steps to be reduced into one operation and one must define predicates to tell, e.g., whether one is within this operation or not. Thus it is hard (though not impossible) to fit the aforementioned program-based reordering approach to our executionbased scenario where basically all local steps may be reordered.

Moreover the reduction theorems presented above require commutativity for steps of a certain program unconditionally and they preserve only global safety properties that may not be influenced by the local reordered steps. Local properties of the program are thus not transferred down. On the other hand in our case reordering can only be done if the steps are local and memory-safe. As memory safety depends on global (the ownership state) and local information (the program state), this property cannot be transferred by the existing reduction theorems. This also holds for the work of Cohen and Lamport [CL98] on reduction in TLA. The latter however introduced the preservation of liveness properties which we do not touch within the frame of this report. It should be also noted that commutativity arguments like the ones we use in the proof of our reduction theorem are closely related to the notion of non-interference in information flow theory [GM82, Rus92]. Simply put, it is argued that an action does not interfere with a certain domain if it can be pruned from a computation without changing results visible in that domain. If this is the case it can be placed elsewhere in the computation, yielding commutativity.

Besides the classic theorems there is more recent work on order reduction. Several specific approaches have been proposed to employ reduction in model checking in order to tackle the problem of state explosion [FQ04, FFQ05, FG05]. Also the formal verification tool VCC [CDH+09] used in the Verisoft XT project relies on order reduction. Threads are verified as if they run sequentially and concurrent actions of other threads are only interleaved before shared memory accesses. A reduction theorem to justify this "coarse scheduling" was proposed and proven [CMST09], however it only covered the existence of a safe equivalent coarse schedule for a given arbitrary safe schedule. The soundness of the methodology, i.e., that also for every unsafe trace there exists an unsafe coarse schedule, remained open. Nevertheless this approach was the inspiration for the reduction theorem presented below. In fact, the VCC reduction theorem can be derived from an instantiation of our general reduction theorem. In contrast we use a different ownership model then the VCC tool. There ownership is based on typed objects while in our model ownership is based on memory addresses. Our ownership model is a simplified version of the one presented by Cohen and Schirmer in order to justify sequential consistent memory for a memory system implementing Total Store Order [CMST09]. Ownership of memory and ownership transfer is not a new concept. It is also used in Concurrent Separation Logic [Bro04].

## 1.3 Notation and Conventions

In the scope of this document we use the following notation and conventions.

# 1.3.1 Types and Records

Types are usually identified by blackboard bold or blackletter font in case their names consist of a single letter. The natural numbers  $\mathbb{N}=\{0,1,2,3,\ldots\}$  contain zero.  $\mathbb{N}^+=\mathbb{N}\setminus\{0\}$  denotes the strictly positive natural numbers.  $\mathbb{N}_i\subset\mathbb{N}$  with i>0 and  $\#\mathbb{N}_i=i$  defines the set of the i smallest natural numbers.

$$\mathbb{N}_i = \{0, \dots, i - 1\}$$

The set of Boolean values  $\{0,1\}$  is represented by  $\mathbb{B}$ . We define new types using the standard mathematical notation where  $\times$  creates tuples and  $\rightarrow$  creates total functions. Partial functions are identified by a  $\rightarrow$  arrow in their type signature. We treat record types as n-tuples where each component  $c_i$  can have a different type  $t_i$ . Let  $r \in R$  be such a record. We can declare it in two equivalent ways:

$$r = (r.c_0 : t_0, \ldots, r.c_{n-1} : t_{n-1})$$

$R = \{c_0 : t_0 ; \ldots ; c_{n-1} : t_{n-1}\}$

Record component can have any type — also records — but we forbid recursive types here. Sometimes we use  $c_i \subseteq t_i$  instead of  $c_i : t_i$  to denote that  $c_i$  is a powerset of  $t_i$  do We introduce a handy record update notation that allows modifying single record components. Let  $U = \bigcup_{i=0}^{m-1} id_i$  be a set of m different component identifiers, representing the components of record r to be updated, i.e.,  $\forall i,j < m.\ i \neq j \Longrightarrow id_i \neq id_j.$  and  $\forall i < m \exists j < n.\ id_i = c_j.$  The new values for the respective components shall be  $v_0$  to  $v_{m-1}$ . Then the updated record r' is defined by:

$$\begin{split} r' = r \llbracket id_0 := v_0; \ id_1 := v_1; \ \dots; \ id_{m-1} := v_{m-1} \rrbracket \\ & \qquad \qquad \\ \forall i < m. \ r'.id_i = v_i \land \forall c \not\in U. \ r'.c = r.c \end{split}$$

## 1.3.2 Propositional Logic

Logical propositions contain conjunction  $\land$ , disjunction  $\lor$ , negation, implication  $\Longrightarrow$ , equivalence  $\Longleftrightarrow$  and brackets. For negation literature knows several symbols.

$$/x \equiv \sim x \equiv \neg x \equiv \overline{x}$$

Here we will use mostly /x and sometimes  $\overline{x}$  where it saves brackets. Definitions and identity is denoted by  $\equiv$ . The priority order  $\prec$  of logical operators used in this document is defined below from weakest to strongest binding.

$$\iff$$

$\prec$   $\implies$   $\prec$   $\lor$   $\prec$   $\land$   $\prec$   $/$

To display voluminous conjunctions and disjunctions in a clear and compact style we introduce a notation to combine all propositions  $p_i$  from a finite set P. For  $P = \emptyset$  we have  $\bigwedge P = 1$  and  $\bigvee P = 0$ . Otherwise:

$$\bigwedge P = \bigwedge \{ p_0, p_1, \dots \} \equiv ((p) \land \bigwedge (P \setminus \{p\})) \quad \text{s.t. } p = \epsilon P$$

$$\bigvee P = \bigvee \{ p_0, p_1, \dots \} \equiv ((p) \lor \bigvee (P \setminus \{p\})) \quad \text{s.t. } p = \epsilon P$$

Here  $\epsilon$  is Hilbert's choice operator that chooses one element out of a given set.

## 1.3.3 Set Notation

In general we use standard set theory, however we extend it by a few shorthand definition. The disjoint union of sets is denoted by  $\cup$ . Let A, B, C be sets of the same type, then:

$$C = A \cup B \iff C = A \cup B \land A \cap B = \emptyset$$

To express that two sets are equal for some element  $\alpha$ , i.e. that  $\alpha$  is either contained or not contained in *both* sets, we choose the following notation

$$A =_{\alpha} A' \equiv \alpha \in A \Leftrightarrow \alpha \in A'$$

If both sets are subset of some superset B, i.e.,  $A, A' \subseteq B$ , we can easily show the property, that if A and A' agree on all elements of B, they must be equal.

$$(\forall \alpha \in B. \ A =_{\alpha} A') \iff A = A'$$

# 1.3.4 Sequences

Moreover in this docoument we will deal excessively with computation sequences. An arbitrary lengthy sequence of elements  $a^i \in \mathbb{A}$  has type  $\mathbb{A}^*$  and is represented by a.

$$\underline{a}: \mathbb{A}^* \iff \underline{a} = \varepsilon \vee \exists a^0 \in \mathbb{A}, \underline{a}'_{\backprime}: \mathbb{A}^*. \ \underline{a} = a^0, \underline{a}'_{\backprime}$$

Let  $\varepsilon$  be the empty sequence, then we define the length of sequences as follows.

$$|\varepsilon| = 0$$

$|a^0, \underline{a}'| = |\underline{a}'| + 1$

For manipulating sequences we define the function pop which removes the first i members of a sequence.

$$pop(\underline{\underline{a}}, i) = \begin{cases} \underline{\underline{a}} & : \quad i = 0\\ pop(\underline{\underline{a}}', i - 1) & : \quad i > 0 \land \underline{\underline{a}} = a^0, \underline{\underline{a}}' \\ \varepsilon & : \quad \text{otherwise} \end{cases}$$

Function tail yields the remainder after removing the head of a sequence.

$$tl(\underline{a}) = pop(\underline{a}, 1)$$

Furthermore we can number the members of a sequence in ascending order starting from the beginning.

$$\underline{\underline{a}} = a^0, a^1, a^2, \dots$$

Consequently we can select finite subsequences of a sequence via interval notation. First of all for  $a \le b$  we introduce the following integer intervals.

$$\begin{array}{llll} [a:b] & \equiv & \{a,a+1,\ldots,b\} \\ (a:b] & \equiv & [a+1:b] \end{array} \qquad \begin{array}{lll} [a:b) & \equiv & [a:b-1] \\ (a:b) & \equiv & [a+1:b-1] \end{array}$$

Now subsequences of  $\underline{x}$  are easily defined recursively. Let  $0 \le a \le b$ , then:

$$\underline{\underline{x}}[a:b] \equiv \begin{cases} x^a & : & a=b \\ x^a, \underline{\underline{x}}[a+1:b] & : & \text{otherwise} \end{cases}$$

For open intervals, e.g.,  $\underline{x}[a:b)$  the equivalent closed interval from above shall be used.

## 1.3.5 Computations

Computations are sequences of configurations from a state space  $\mathbb{S}$ . They rely on transition function  $\delta$  that transform the state using inputs from some domain  $\mathbb{I}$ :

$$\delta: \mathbb{S} \times \mathbb{I} \to \mathbb{S}$$

A computation  $\underline{s}:\mathbb{S}^*$  for input sequence  $\underline{in}=in^0,in^1,in^2,\ldots:\mathbb{I}^*$  is represented by the shorthand  $\underline{s}_{\delta,in}$ .

$$\underline{\underline{s}}_{\delta,in} \equiv s^0, s^1, s^2, \dots$$

s.t.  $\forall j \ge 0. \ s^{j+1} = \delta(s^j, in^j)$

To denote state transitions we us the following arrow notation for  $i, n \in \mathbb{N}$ .

$$s^{i} \longrightarrow_{\delta,in}^{n} s^{i+n} \equiv \begin{cases} s^{i+1} = \delta(s^{i}, in^{i}) \wedge s^{i+1} \longrightarrow_{\delta,in}^{n-1} s^{i+n} & : \quad n > 0 \\ 1 & : \quad n = 0 \end{cases}$$

It can be generalized for states  $s, s' \in \mathbb{S}$  omitting the index i.

$$s \longrightarrow_{\delta,in}^{n} s' \equiv \exists \underline{a} : \mathbb{S}^*. a^0 \longrightarrow_{\delta,in}^{n} a^n \wedge s = a^0 \wedge s' = a^n$$

There are two special versions of this:

$$s \longrightarrow_{\delta,in} s' \equiv s \longrightarrow_{\delta,in}^{1} s'$$

$s \longrightarrow_{\delta,in}^{*} s' \equiv \exists n. \ s \longrightarrow_{\delta,in}^{n} s'$

Given some particular input  $x \in \mathbb{I}$  we also use  $s \longrightarrow_{\delta,x} s'$  instead of  $s' = \delta(s,x)$ . Implicite conversion is possible between n+1-tuples of sequences and sequences of n+1-tuples with the same length m+1.

$$\begin{array}{cccc} (\underline{in_0}, \dots, \underline{in_n}) & = & ([in_0^0, \dots, in_0^m], \dots, [in_n^0, \dots, in_n^m]) \\ & \updownarrow & & \updownarrow \\ (\underline{in_0}, \dots, in_n) & = & (in_0^0, \dots, in_n^0), \dots, (in_0^m, \dots, in_n^m) \end{array}$$

This is useful for transition functions that take more than one input. If in is for instance a triple (a,b,c) by the implicite conversion  $(\updownarrow)$  we can still use the arrow notation to denote an n-step transition from s to s' under the input sequences  $(\underline{a},\underline{b},\underline{c})$  and so forth. We write:

$$s \longrightarrow_{\delta,a,b,c,\dots}^{n} s'$$

# 2 Concurrent Machine Model with Shared Memory and Ownership

In order to model multiprocessor systems later we first introduce a general model for machines that are concurrently accessing a shared memory. We speak of a **Co**ncurrent system with shared **m**emory and **o**wnership (*Cosmos*). Accesses are governed by an ownership policy guaranteeing sound memory accesses i.e., the absence of data races on the shared memory. The ownership model builds on previous work by Cohen and Schirmer. There it was used to

ensure sequential consistency for a shared memory system with store buffers (TSO). Here we use it to show a reordering theorem were arbitrary interleavings of machine steps are reordered into a coarse schedule of blocks of machine steps, were each block starts with a shared memory access and may be followed by local computations. In the model presented below each machine can be instantiated arbitrarily. However for each instantiation a program logic has to be provided in terms of safety conditions on the machine transitions in order to ensure memory soundness and maintain ownership invariants. We first define the *Cosmos* model in general where machines are only communicating via shared memory. Later on we extend the model with inputs, outputs and visible components. Afterwards we will formulate and proof the reordering theorem and instantiate the *Cosmos* model with a generic ISA model to obtain a Multiprocessor ISA Model with Ownership.

# 2.1 Configuration and Parameters

We consider a *Cosmos* model with type  $\mathbb{C}$ , which is a concurrent system of  $np \in \mathbb{N}$  generic machines and a shared memory with the address range  $\mathfrak{A}$ . Note that on the top level we only consider the memory shared between the machines in the *Cosmos* model . Other communication must be handled internally.

A machine p is modelled as an Moore Automata without inputs or outputs for now as explained above. Machines could be devices, processors or even Cosmos models themselves. To develop a model as general as possible we parametrize it by a number of system parameters and types. These polymorphic types shall be identified by gothic font. Functions and values declared based on these types are also polymorphic and must be instantiated for a particular system. All components related to ownership or program logics are printed using calligraphic font.

A configuration  $C \in \mathbb{C}$  has three components (C.s, C.m, C.S):

- $C.s: \mathbb{N}_{np} \to \mathbb{S}$  the state of each machine in the system, state C.s[p] of machine p is a record with two components:

- $C.s[p].\mathcal{O}\subseteq\mathfrak{A}$  the set of addresses owned by machine p. Owned addresses may only be modified by their owner.

- $C.s[p].c \in \mathfrak{C}_p$  the configuration of machine p, where  $\mathfrak{C}_p$  is an instantiable machine configuration type. Some components in  $\mathfrak{C}_p$  may be defined to be visible to (but not modifiable by) other machines.

- $C.m : \mathbb{M}$  the memory shared by all machines in the system,  $\mathbb{M} = \mathfrak{A} \to \mathfrak{V}$ , where  $\mathfrak{V}$  denotes the range of values for memory cell contents.

- $C.S \subseteq \mathfrak{A}$  the set of shared writable addresses. Shared addresses can be owned or unowned. In the first case they can only be read by machines other than the owner.

We use the following shortcuts for state components:

Primed, accented or indexed versions of these abbreviations translate in the obvious way to the functions taking the corresponding version of argument C e.g.,  $\hat{c}^i_p = c_p(\hat{C}^i)$ .

In addition to np,  $\mathfrak{A}$ ,  $\mathfrak{V}$  and the configuration types  $\mathfrak{C}_p$  we have the following *Cosmos* model system parameters:

- $\delta_p : \mathbb{C} \times \mathbb{N}_{np} \to \mathbb{C}^p$  for  $p \in \mathbb{N}_{np}$  a transition function for machine p.

- $\mathcal{R} \subseteq \mathfrak{A}$  the set of read-only addresses. Such addresses are neither shared writable, nor owned by any machine

- $\sqrt{p}:\mathbb{C}\to\mathbb{B}$  for  $p\in\mathbb{N}_{np}$  a program logic to determine safe steps of machine p wrt. ownership and further safety conditions

- $\mathcal{IO}_p : \mathbb{C} \times \mathbb{N}_{np} \to \mathbb{B}$  for  $p \in \mathbb{N}_{np}$  a predicate based on the program logic of machine p identifying  $\mathcal{IO}$  steps in the next transition of p depending on its inputs. For example  $\mathcal{IO}$  steps include but are not limited to all reads or writes on shared writable memory.

- $reads_p, writes_p : \mathbb{C} \times \mathbb{N}_{np} \to 2^{\mathfrak{A}}$  for  $p \in \mathbb{N}_{np}$  functions yielding the sets of memory addresses read and written by machine p in its next step under the specified inputs.

In the declarations above  $\mathbb{C}^p$  stands for the records type of the configuration that transition function  $\delta_p$  produces. It is a projection of a full configuration C containing all machine states to a configuration  $C|_p$  which only contains the state for machine p. The projection function  $\cdot|_p : \mathbb{C} \times \mathbb{N}_{np} \to \mathbb{C}^p$  is formally defined as:

$$C|_{p} = \{C|_{p}.s, C|_{p}.m, C|_{p}.\mathcal{S}\} \qquad \text{s.t.} \qquad \bigwedge \left\{ \begin{array}{l} C|_{p}.s = C.s[p], \\ C|_{p}.m = C.m, \\ C|_{p}.\mathcal{S} = C.\mathcal{S} \end{array} \right\}$$

Note that in the Cohen-Schirmer theory  $\mathcal{IO}$  memory instructions are denoted as *volatile* accesses. However to avoid confusion with the notion of volatile accesses on the C level we rename the concept here. Actually there is a close connection between volatile and  $\mathcal{IO}$  accesses, as there are certain compiler requirements for all accesses that are compiled to ISA  $\mathcal{IO}$  operations. In fact all volatile accesses on the C level become  $\mathcal{IO}$  accesses on the ISA level. Nevertheless they are not congruent i.e., there might be more  $\mathcal{IO}$  accesses which do not stem from volatile memory operations. We will see this later on.

In contrast to the Cohen-Schirmer model we also confined ourselves to treat the read-only addresses as a fixed parameter of the system. In the scope of this thesis we assume that the concurrent system we are focusing on is already initialized and after that point the read-only addresses should be constant. This implies a restriction of ownership transfer after the initialization phase i.e., no read-only addresses may be acquired by machines and all released addresses must stay writable. The restriction is motivated by the reordering proof further below. If addresses may be put in or taken out of the  $\mathcal R$  set, there needs to be a synchronization policy between the machines governing when it is safe to

acquire or release read-only addresses. If the set of read-only addresses was not fixed we would actually have to deal with an ordinary shared memory and all the complexity it is accompanied by. As we can think of little application scenarios of temporary read-only addresses, besides self-modifying code, we just omit this possibility here. Note that the initialization of concurrent systems is usually achieved in a sequential manner where only a single processor is active. Hence a different model must be considered to treat this case anyway.

### 2.2 Semantics

Now we will define the transition function  $\Delta$  of the overall system. It computes the next state for a system step in a computation  $\underline{C}$  which is based on the schedule  $\underline{\sigma}$ . We need a notation  $C\lceil d\rceil_p$  to embed projected configurations  $d\in\mathbb{C}^p$  in *Cosmos* model configurations  $C\in\mathbb{C}$ .

$$C[d]_p = C[m := d.m; s[p] := d.s; S := d.S]$$

Then we define  $\Delta$  for a step of p as follows.

$$\Delta(C, p) = C[\delta_p(C, p)]_p$$

Machine p is chosen according to schedule  $\underline{\sigma}$  and transition function  $\delta_p$  is computing the resulting projected configuration. The components of the *Cosmos* model configuration are updated accordingly. By construction a machine cannot alter the states of other machines including their ownership sets. There are more restrictions on the instantiation of *Cosmos* model parameters and their interaction defined in the next section.

## 2.3 Parameter Constraints

Not all parameters of a *Cosmos* model can be instantiated arbitrarily, in fact there are several constraints that must be discharged by an instantiation. The constrained instantiable parameters for the system without inputs, outputs and visible components are  $\delta_p$ ,  $\mathcal{IO}_p$ ,  $writes_p$  and  $reads_p$ .

Firstly, the step functions should be deterministic, i.e., no  $\delta_p$  should make any non-deterministic choices. Secondly steps of p must not depend on components in other machines. Formally we collect these conditions in  $constr_{\delta}(p)$ . In the following let  $R = reads_p(C, p)$  and  $W = writes_p(C, p)$ .

$$\frac{C \sim_p^R C' \Longrightarrow C\lceil \delta_p(C,p) \rceil_p \sim_p^W C'\lceil \delta_p(C',p) \rceil_p}{C, C' \in \mathbb{C} \vdash constr_{\delta}(p)}$$

Here the equality of information accessed by p (excluding visible components of other machines) is denoted by the relation  $C \sim_p^A C'$  for sets of memory addresses  $A \subseteq \mathfrak{A}$ . Below we define several equivalence relations for different

Cosmos model components.

$$\begin{array}{lll} C \overset{\sim}{\sim} (A) \ C' & \equiv & \forall adr \in A. \ C.m(adr) = C'.m(adr) \\ C \sim_p^A C' & \equiv & C.s[p] = C'.s[p] \land C \overset{m}{\sim} (A) \ C' \\ C \sim_p C' & \equiv & C \sim_p^{\mathcal{D}_p \cup \mathcal{R}} \ C' \\ C \overset{\circ}{\sim} C' & \equiv & C.\mathcal{S} = C'.\mathcal{S} \land C \overset{m}{\sim} (C.\mathcal{S}) \ C' \\ C \overset{\circ}{\sim} C' & \equiv & \forall p \in \mathbb{N}_{np}. \ \mathcal{O}_p = \mathcal{O}_p' \land C.\mathcal{S} = C'.\mathcal{S} \\ C \overset{\circ}{\sim}_p C' & \equiv & \mathcal{O}_p = \mathcal{O}_p' \land \mathcal{O}_p \cap C.\mathcal{S} = \mathcal{O}_p' \cap C'.\mathcal{S} \end{array}$$

The relation  $C \sim_p C'$  denotes the equality of machine state and locally visible memory. The equality of shared memory is given by  $C \stackrel{s}{\sim} C'$ , while  $C \stackrel{o}{\sim} C'$  talks about the ownership state. The local versions of this relation for machine p is denoted by  $C \stackrel{o}{\sim}_p C'$ . It states that the ownership configuration of p is equivalent in to systems C and C' iff p owns the same addresses and these are partitioned identically into shared and local addresses. We quickly observe:

**Corollary 1** Examining the definitions of  $\stackrel{\circ}{\sim}$  and  $\stackrel{\circ}{\sim}_p$  we see that  $C \stackrel{\circ}{\sim} C'$  implies  $C \stackrel{\circ}{\sim}_p C'$  for all p.

Moreover we require that the functions  $reads_p$  and  $writes_p$  should only rely on the local configuration of machine p

$$\frac{C \sim_p^R C' \Longrightarrow \bigwedge \left\{ \begin{array}{l} reads_p(C,p) = reads_p(C',p), \\ writes_p(C,p) = writes_p(C',p) \end{array} \right\}}{C,C' \in \mathbb{C} \vdash constr_{pred}(p)}$$

In the same way we demand that  $\mathcal{IO}_p$  depends only on the state and local memory of machine p. Thus the program logic for p does not rely on the state of other machines or the contents of shared writable memory.

$$\frac{C \sim_p^R C' \implies \mathcal{IO}_p(C, p) = \mathcal{IO}_p(C', p)}{C, C' \in \mathbb{C} \vdash constr_{\mathcal{IO}}(p)}$$

Finally we are revisiting the  $writes_p$  predicate. Naturally all memory cells not written by a machine step should maintain their values.

$$\forall adr \in \mathfrak{A} \setminus writes_p(C, p). \ \delta_p(C, p). m(adr) = C.m(adr)$$

$$C \in \mathbb{C} \vdash constr_{mem}(p)$$

# 2.4 Sound Memory Accesses and Ownership Invariants

With the ownership model consisting of  $\mathfrak{A}$ ,  $\mathcal{O}_p$ ,  $\mathcal{R}$  and  $\mathcal{S}$  we are imposing restrictions on the possible execution traces  $\underline{C}_{\Delta,\sigma}$  in order to be able to perform reordering later. The predicate sound(C,p) collects all necessary conditions, i.e., the access policy enforced by a consistent ownership configuration for memory accesses. We treat the cases of  $\mathcal{IO}$  and local steps separately and start with the local, i.e., non- $\mathcal{IO}$  steps of machine p.

$$\begin{array}{ccc} /\mathcal{IO}_p(C,p) & reads_p(C,p) \subseteq \mathcal{O}_p \cup \mathcal{R} & writes_p(C,p) \subseteq \mathcal{O}_p \setminus C.\mathcal{S} \\ & \mathcal{O}_p(\Delta(C,p)) = \mathcal{O}_p(C) & \Delta(C,p).\mathcal{S} = C.\mathcal{S} \\ & sound(C,p) \end{array}$$

All addresses being accessed in a local machine step must be either owned or read-only. To shared writable addresses which are owned by p and read-only addresses just reads are allowed in case of non- $\mathcal{IO}$  steps. Also the ownership configuration must stay constant for local operations.

$\mathcal{IO}$  step memory accesses may additionally target all shared read-write addresses but must not write them if they are owned by another machine. Ownership transitions of p are enabled but must not modify the sets of shared addresses owned by other machines.

$$\frac{\mathcal{IO}_p(C) \quad \forall p' \neq p. \ \mathcal{O}_{p'} \cap \Delta(C, p).\mathcal{S} = \mathcal{O}_{p'} \cap C.\mathcal{S} }{reads_p(C) \subseteq \mathcal{O}_p \cup C.\mathcal{S} \cup \mathcal{R} \quad writes_p(C) \subseteq \mathcal{O}_p \cup C.\mathcal{S} \setminus \bigcup_{p' \neq p} \mathcal{O}_{p'} }$$

$$sound(C, p)$$

Additionally there are aforementioned consistency conditions between the ownership sets and the sets of shared addresses, which must be maintained by all transitions of the ownership configuration. For *Cosmos* models we denote these invariants by the predicate  $inv : \mathbb{C} \to \mathbb{B}$ :

$$\forall p, p'. \ p \neq p' \Longrightarrow \mathcal{O}_p \cap \mathcal{O}_{p'} = \emptyset \quad \forall p. \ \mathcal{O}_p \cap \mathcal{R} = \emptyset$$

$$\forall adr \in \mathfrak{A}. \ (\nexists p. \ adr \in \mathcal{O}_p) \Longrightarrow adr \in C.\mathcal{S} \cup \mathcal{R} \quad C.\mathcal{S} \cap \mathcal{R} = \emptyset$$

$$inv(C)$$

The consistency conditions here include the disjointness of ownership sets and that shared read-only addresses can not be owned or shared read-write. Also all unowned addresses must be either shared writable or read-only.

# 2.5 Safety Conditions

Similar to the safety conditions in the store buffer reduction theorem every instantiation has to define constraints on the instructions and their effects on the ownership model in order to guarantee valid configurations of the ghost components and to enforce among others sound memory accesses wrt. ownership. These safety conditions can be defined similarly to the ones in the Cohen-Schirmer model. For every machine p we require a safety judgement  $\sqrt{p}$  on configurations  $C \in \mathbb{C}$  depending on a set  $R \subseteq Ad$  of read-only addresses as well as the total number of machines in the system. The safety conditions are defined wrt. an address space  $Ad \subseteq \mathfrak{A}$ .

$$R, Ad, n \vdash C \checkmark_p$$

Whenever a configuration is considered safe according to the safety judgement all possible steps out of that configuration must preserve the ownership invariants of the system and perform only sound transitions. Hence the correctness of the individual safety conditions must be proven for each instantiation. Let safe(C,p) denote the safety wrt.  $\sqrt{p}$  of a step of machine p in configuration C under external inputs ext.

$$safe(C, p) \equiv \mathcal{R}, \mathfrak{A}, np \vdash C_{\sqrt{p}}$$

For the safety conditions we have to prove aforementioned lemma that all safe steps are sound and are preserving ownership invariants.

$$\forall p < np. \ inv(C) \land safe(C, p) \Longrightarrow sound(C, p) \land inv(\Delta(C, p))$$

On the top level it is not defined how the ownership can be transfered between machines, however the safety conditions of p must guarantee that inv(C) is preserved when p manipulates the ownership configuration. Similar to the  $\mathcal{IO}_p$  predicate there is a constraint on the safety judgement that it should rely on system components and visible memory as well as the ownership configuration and machine outputs during steps of p.

$$\begin{aligned} constr_{safe}(p) &\equiv \\ \forall C, C' \in \mathbb{C}. \\ C \sim_p C' \wedge \begin{cases} C \stackrel{\circ}{\sim}_p C' & : & /\mathcal{IO}_p(C) \\ C \stackrel{\circ}{\sim} C' & : & \mathcal{IO}_p(C) \end{cases} \implies safe(C, p) = safe(C', p) \end{aligned}$$

Thus we have a model that governs a concurrent execution  $\underline{C}_{\delta,\sigma}$  by ownership and safety conditions. Accesses to shared resources must be marked as special  $\mathcal{IO}$  operations representing, e.g., atomic memory instructions in case of multicore processor systems. Local operations can only target owned unshared data that is not observable by other machines. Therefore it is possible to reorder these local steps as will be seen later on. First we extend our system with further means of communication.

# 3 Inputs, Outputs and Visible Components

Until now the only way for machines in our system to communicate is via the shared memory. While this is a convenient model it does not reflect the reality of many existing concurrent systems. In fact there might also be communication via interrupts, bus connections, I/O port registers and the like. Last but not least there may be external inputs and outputs of the system. In the following we strive to model these means of communication in a way as general as possible, so that it can be instantiated arbitrarily afterwards.

## 3.1 Additional Parameters

We extend our automaton model for a machine p with inputs in  $\mathfrak{I}_p \subseteq \mathbb{O} \cup \mathfrak{E}$  and outputs using the alphabet  $\mathfrak{O}_p$ . Here  $\mathfrak{E}$  represents external inputs to the system while  $\mathbb{O}$  is the union of the outputs of all machines inside the system.

$$\mathbb{O} \equiv \bigcup_{p \in \mathbb{N}_{np}} \mathfrak{O}_p$$

For the new setting we have to update the following *Cosmos* model system parameters, as they also depend on inputs now.

- $\delta_p: \mathbb{C} \times \mathbb{N}_{np} \times 2^{\mathfrak{I}_p} \to \mathbb{C}^p \text{ for } p \in \mathbb{N}_{np}$

- $\mathcal{IO}_p: \mathbb{C} \times \mathbb{N}_{np} \times 2^{\mathfrak{I}_p} \to \mathbb{B} \text{ for } p \in \mathbb{N}_{np}$

- $reads_p, writes_p : \mathbb{C} \times \mathbb{N}_{np} \times 2^{\mathfrak{I}_p} \to 2^{\mathfrak{A}}$  for  $p \in \mathbb{N}_{np}$

We introduce new parameters below.

- $\omega_p: \mathbb{C} \to 2^{\mathfrak{D}_p}$  for  $p \in \mathbb{N}_{np}$  the output function for machine p which may depend not only on C.m and  $c_p$  but also on visible components of other machines' states.

- $\stackrel{v}{\sim}_p \subseteq \mathfrak{C}_p \times \mathfrak{C}_p$  for all  $p \in \mathbb{N}_{np}$  an equivalence relation implicitely encoding which components of machine configuration  $c_p$  are visible to other machines. Iff all these components are equal in two configurations of machine p then the relation holds.

- $vis_p: \mathbb{C} \times \mathbb{N}_{np} \times 2^{\mathfrak{I}_p} \to \mathbb{B}$  predicate signaling that the next step of machine p accesses visible state components of any other machine.

We have introduced visible components above, on which the execution of other machines may depend. Thus we are extending the notion of sharing from memory addresses to machine components. This is useful when we consider, e.g., virtual machines that are not virtualized completely, i.e., some components of the underlying hardware are shared explicitly. Also for interrupts we will see later on that certain processor registers can be shared between the interruptible program and its interrupt handler. Thus for every machine p a subset of components may be visible and each update of these components by p or steps by other machines depending on them must be considered  $\mathcal{IO}$  steps.

Furthermore observe that the function  $\omega_p$  is defined on the complete state of the system. We will later restrict the outputs generated by it to depend on the visible compents and shared memory. Nevertheless they are inherently Mealy output signals of machine p wrt. the inputs of other machines, i.e., they might change even if p is not making a step. In contrast the visible components of p can only change in a  $(\mathcal{IO})$  step of p. Hence we can consider them as the Moore outputs of machine p.

## 3.2 Extended Semantics

We also have to extend the transition function  $\Delta$  of the overall system. A computation  $\underline{C}$  of a CSO now also depends on an external input sequence  $\underline{ext}$ . Moreover we have to map the corresponding inputs to the machine p that takes the next setp. We define Delta for a step of p under external input ext as follows.

$$\Delta(C, p, ext) = C[\delta_p(C, p, in(C, p, ext))]_p$$

The inputs to machine p are calculated from the outputs of all machines and the external inputs by the function in(C, p, ext) as defined below.

$$in(C, p, ext) \equiv \left(\bigcup_{p' \in \mathbb{N}_{np}} \omega_{p'}(C) \cup ext\right) \cap \mathfrak{I}_p$$

Considering computations  $\underline{C}$ ,  $\underline{\sigma}$ ,  $\underline{ext}$  we also write  $in_p(C^i)$  for  $in(C^i, p, ext^i)$ . Note that  $\underline{ext}$  may contain external inputs for machines that are not currently scheduled. These inputs do not influence the execution of the system and are thus redundant. However to keep the model simple we do not restrict the external input sequence but allow it to contain arbitrary irrelevant inputs.

# 3.3 Updated Parameter Constraints

The constraints on the parameters introduced before must be adapted to the new situation where we have input and output signals as well as visible components. Furthermore we need to constrain the new parameters  $\mathfrak{I}_p$ ,  $\mathfrak{O}_p$ ,  $\omega_p$ ,  $\overset{v}{\sim}_p$  and  $vis_p$ .

The step function of p may now also depend on visible components of others. Such accesses are denoted by the  $vis_p$  predicate. We update  $constr_{\delta}(p)$  using the abbreviations  $R = reads_p(C, p, in)$  and  $W = writes_p(C, p, in)$ .

$$\frac{\bigwedge \left\{ \begin{matrix} C \sim_p^R C', \\ vis_p(C, p, in) \Rightarrow C \stackrel{v}{\sim} C' \end{matrix} \right\} \Longrightarrow C\lceil \delta_p(C, p, in) \rceil_p \sim_p^W C'\lceil \delta_p(C', p, in) \rceil_p}{C, C' \in \mathbb{C}, in \subseteq \mathfrak{I}_p \vdash constr_{\delta}(p)}$$

Here the equality of all visible components is denoted by the relation  $C \stackrel{v}{\sim} C'$ . We also define the relation  $C \stackrel{sv}{\sim} C'$  which states the consistency of the shared state in the system (excluding read-only addresses).

$$C \overset{v}{\sim} C' \equiv \forall p \in \mathbb{N}_{np}. \ c_p \overset{v}{\sim}_p \ c'_p$$

$$C \overset{v}{\sim} C' \equiv C \overset{s}{\sim} C' \wedge C \overset{v}{\sim} C'$$

In same way the functions and predicates  $reads_p$ ,  $writes_p$  and  $vis_p$  should only rely on the local configuration of machine p

$$C \sim_p^R C' \Longrightarrow \bigwedge \left\{ \begin{aligned} reads_p(C, p, in) &= reads_p(C', p, in), \\ writes_p(C, p, in) &= writes_p(C', p, in), \\ vis_p(C, p, in) &= vis_p(C', p, in) \end{aligned} \right\}$$

$$C, C' \in \mathbb{C}, in \subseteq \mathfrak{I}_p \vdash constr_{pred}(p)$$

As another parameter constraint  $\stackrel{v}{\sim}_p$  has to be an equivalence relation.

$$c_p \stackrel{v}{\sim}_p c_p \qquad c_p \stackrel{v}{\sim}_p c'_p \Longrightarrow c'_p \stackrel{v}{\sim}_p c_p \qquad c_p \stackrel{v}{\sim}_p c'_p \wedge c'_p \stackrel{v}{\sim}_p c''_p \Longrightarrow c_p \stackrel{v}{\sim}_p c''_p$$

$$C, C', C'' \in \mathbb{C} \vdash constr_v(p)$$

Moreover we assume that every output or external input is at most handled by one machine in the *Cosmos* model so that there are no races on the reaction to input signals i.e.:

$$\frac{\forall p' \in \mathbb{N}_{np}. \ p \neq p' \Longrightarrow \mathfrak{I}_p \cap \mathfrak{I}_{p'} = \emptyset}{constr_{\mathfrak{I}}(p)}$$

Similarly we demand that all outputs and external inputs are unique. We only consider internal Mealy output signals here.

$$\mathfrak{O}_{p} \cap \mathfrak{E} = \emptyset \quad \forall p' \in \mathbb{N}_{np}. \ p \neq p' \Longrightarrow \mathfrak{O}_{p} \cap \mathfrak{O}_{p'} = \emptyset \\

\forall \alpha \in \mathfrak{O}_{p}. \ \exists p' \in \mathbb{N}_{np}. \ \alpha \in \mathfrak{I}_{p'} \\

\hline

constr_{\mathfrak{O}}(p)$$

We restrict the output functions as follows.

$$\frac{c_p = c_p' \wedge c_{p'} \stackrel{v}{\sim}_{p'} c_{p'}' \Longrightarrow \omega_p(C) =_{\alpha} \omega_p(C')}{\omega_p(C) =_{\alpha} \omega_p(C') \wedge c_p = c_p'' \wedge c_p' = c_p''' \wedge c_{p'}' \stackrel{v}{\sim}_{p'} c_{p'}'' \Longrightarrow \omega_p(C'') =_{\alpha} \omega_p(C''')}{C, C', C'', C''' \in \mathbb{C}, p', \alpha \in \mathfrak{D}_p \cap \mathfrak{I}_{p'} \vdash constr_{\omega}(p)}$$

In general the constraint implies that the generated outputs of p for any machine p' depend only on the machine state of p and the visible components of p'. Additionally the behaviour of output signals in case p does not make a step must be predictable from the changes in the visible components of the receiver. Later on we will also demand that outputs must be kept active until a reaction of a receiver via a change in the visible components is detected.

In order to identify situations when machine p reacts to an input (e.g. by starting an interrupt handler) we introduce the following predicate.

$$reacts(C, p, in) \equiv \delta_p(C, p, in) \neq \delta_p(C, p, \emptyset)$$

We detect such a situation by comparing the next configuration wrt. the actual inputs to one where all inputs are deactivated. When a deterministic machine changes its configuration differently for a given input, then it must have been in reaction to that input. Such situations represent a communication with the environment, therefore we consider them as  $\mathcal{IO}$  steps, too.

Another property we will need is that reactions for the same inputs only depend on the configuration of machines (e.g. interrupt mask registers, APIC state etc.). Also inputs do not cancel out each other i.e., whenever there is a reaction to an input, no matter how much more inputs we add the machine will still react to one of them. Note that by construction machines only react to their personal inputs.

$$\frac{c_p = c_p' \Longrightarrow reacts(C, p, in) = reacts(C', p, in)}{/reacts(C, p, in) \land in' \subseteq in \Longrightarrow /reacts(C, p, in')}$$

$$C, C' \in \mathbb{C}, in, in' \subseteq \mathfrak{I}_p \vdash constr_{react}(p)$$

In addition  $\mathcal{IO}_p$  must be redefined such that all reactions to inputs are also considered  $\mathcal{IO}$  steps. Reacting to an input is part of a machine's communication with its environment, thus we model it as an  $\mathcal{IO}$  operation. Moreover local steps stay local if their configurations are locally equivalent and there are not more inputs than in the original step. With R defined as above:

$$C \sim_{p}^{R} C' \implies \mathcal{IO}_{p}(C, p, in) = \mathcal{IO}_{p}(C', p, in)$$

$$reacts(C, p, in) \implies \mathcal{IO}_{p}(C, p, in)$$

$$\forall in' \subseteq in. /\mathcal{IO}_{p}(C, p, in) \land C \sim_{p}^{R} C' \implies /\mathcal{IO}_{p}(C', p, in')$$

$$C, C' \in \mathbb{C}, in \subseteq \mathfrak{I}_{p} \vdash constr_{\mathcal{IO}}(p)$$

At last we add inputs to the constraint on the  $writes_p$  predicate.

$$\forall adr \in \mathfrak{A} \setminus writes_p(C, p, in). \quad \delta_p(C, p, in). m(adr) = C.m(adr)$$

$$C \in \mathbb{C}, in, \subseteq \mathfrak{I}_p \vdash constr_{mem}(p)$$

With the updated parameter constraints defined we can now turn to the soundness conditions for the extended *Cosmos* model with inputs, outputs and visible components.

<sup>&</sup>lt;sup>4</sup>This means that we do not consider memory mapped I/O ports to be part of shared memory. Such ports shall be part of the visible components of machines so that other machines may react to changes of them by their outputs also when they are not stepped. Note that this setting restricts *Cosmos* models to systems where I/O ports are not shared between different machines and there are fixed pairs of communication partners.

# 3.4 Soundness for Inputs, Outputs and Visible Components

The predicate sound(C, p, ext) collects all necessary soundness conditions for the new system with (external) inputs, outputs and visible components. It is an extension of sound(C, p) which is implied by sound(C, p, ext). Again we treat the cases of  $\mathcal{IO}$  and local steps separately. First we define a shorthand pattern for commonly used predicates of the form  $pred_p(C, p, in)$ .

$$pred_p(C) \equiv pred_p(C, p, in(C, p, ext))$$

Now we consider the local i.e. non- $\mathcal{IO}$  steps of machine p.

$$\begin{array}{ll}

/\mathcal{IO}_p(C) & reads_p(C) \subseteq \mathcal{O}_p \cup \mathcal{R} & writes_p(C) \subseteq \mathcal{O}_p \setminus C.\mathcal{S} \\

c_p(\Delta(C, p, ext)) \stackrel{v}{\sim}_p c_p & \omega_p(\Delta(C, p, ext)) = \omega_p(C) & /vis_p(C) \\

\mathcal{O}_p(\Delta(C, p, ext)) = \mathcal{O}_p(C) & \Delta(C, p, ext).\mathcal{S} = C.\mathcal{S} \\

\hline

sound(C, p, ext)

\end{array}$$

In addition to the shared memory access restrictions for non- $\mathcal{IO}$  steps, machines in this case may not alter visible components. Also local steps may not depend on visible components of others. In general the outputs of all machines in the system are not allowed to change for local steps of p and by construction p does not react to the inputs from other machines.

$$\mathcal{IO}_{p}(C) \qquad \alpha \in \omega_{p}(C) \setminus \mathfrak{I}_{p} \Longrightarrow \alpha \in \omega_{p}(\Delta(C, p, ext))$$

$$\forall p' \neq p. \ \mathcal{O}_{p'} \cap \Delta(C, p, ext). \mathcal{S} = \mathcal{O}_{p'} \cap C.\mathcal{S}$$

$$reads_{p}(C) \subseteq \mathcal{O}_{p} \cup C.\mathcal{S} \cup \mathcal{R} \qquad writes_{p}(C) \subseteq \mathcal{O}_{p} \cup C.\mathcal{S} \setminus \bigcup_{p' \neq p} \mathcal{O}_{p'}$$

$$sound(C, p, ext)$$

In  $\mathcal{IO}$  steps machine outputs must not be deactivated unless they are targetting themselves only which is benign. Besides that we have the same restrictions for  $\mathcal{IO}$  steps as before. The ownership invariants are not touched by the introduction of the additional ways of communication.

# 3.5 Extended Safety Conditions

We also have to consider inputs  $in \subseteq \mathfrak{I}_p$  in the program logic for p now.

$$R, Ad, n, in \vdash C \sqrt{n}$$

Furthermore safe(C, p, ext) denotes the safety wrt.  $\sqrt{p}$  of a step of machine p in configuration C under external inputs ext.

$$safe(C, p, ext) \equiv \mathcal{R}, \mathfrak{A}, np, in_p(C) \vdash C \checkmark_p$$

We write  $safe_p(C^i)$  instead of  $safe(C^i,p,ext^i)$  for all i whenever it is unambiguous and we are considering computations  $\underline{C}, \underline{\sigma}, \underline{ext}$  with  $\sigma^i = p$ . Similarly  $safe_p(C)$  and  $safe_p(C')$  is short for safe(C,p,ext), and safe(C',p,ext) respectively. The safety lemma to be proven for every instantiation is stated below.

**Lemma 1** (Correctness of Safety Conditions) We consider a Cosmos model configuration  $C^i$  and its next state  $C^{i+1}$  that was reached by a step of any machine p under

external inputs  $ext^i$  obeying its safety conditions. If ownership invariants were fulfilled before the step, all memory accesses of the step are sound and we again have a configuration where invariants hold.

$$\forall p < np. \ inv(C^i) \land safe_p(C^i) \Longrightarrow sound(C^i, p, ext^i) \land inv(C^{i+1})$$

We also update  $constr_{safe}(p)$  by taking inputs into account. As local steps are by definition never reacting to inputs safety can in this case be transferred to systems where we have the same local configuration but potentially less inputs using  $constr_{react}(p)$ . Only if we have more inputs a local step can become an unsafe  $(\mathcal{IO})$  step. When examining the safety of  $\mathcal{IO}$  steps in related system configurations identical inputs must be taken into account.

$$\begin{aligned} constr_{safe}(p) &\equiv \\ \forall C, C' \in \mathbb{C}, ext \subseteq \mathfrak{E}. \\ C \sim_p C' \wedge \begin{cases} C \stackrel{\circ}{\sim}_p C' \wedge in(C', p, ext) \subseteq in_p(C) &: /\mathcal{IO}_p(C) \\ C \stackrel{\circ}{\sim} C' \wedge in(C', p, ext) = in_p(C) &: \mathcal{IO}_p(C) \end{cases} \\ &\Longrightarrow safe_p(C) = safe(C', p, ext) \end{aligned}$$

This finishes the *Cosmos* model definition and we focus on reordering in the following.

# 4 *IO*-Block Schedule Reordering

The ownership model introduced for *Cosmos* models allows us not only to impose safety conditions for sound concurrent memory accesses by the machines of the system. It also allows for a reordering of machine steps in the concurrent model. In the following we will provide theorems exploiting this fact in order to reduce the interleaving of machines and justify the assumption of coarse scheduling. We want to consider schedules where there are interleaved blocks of execution steps of a single machine p. Each such block starts with p performing an  $\mathcal{IO}$  operation which is followed by a sequence of local computations. Such blocks we call  $\mathcal{IO}$ -blocks. Having a schedule interleaving only such  $\mathcal{IO}$ -blocks is convenient for Multiprocessor ISA machines when we want to apply compiler consistency and go up to the C and Assembly level later on. However it also applies to the modelling of systems with devices as well as preemptive threads running concurrently on the same processor. Moreover it justifies the concurrent verification approach of tools like VCC.

## 4.1 IO-Block Schedules

Given a *Cosmos* model computation  $\underline{C}_{\Delta,\sigma,ext}$  and a machine p we already defined the predicate  $\mathcal{IO}(C^i,\sigma^i,ext^i)$  which states that in configuration  $C^i$  machine  $\sigma^i$  is at an  $\mathcal{IO}$ -point. Such  $\mathcal{IO}$  accesses are usually used to access memory shared with other machines and for other atomic actions that have systemwide effects. As there are specific compiler optimization restrictions for these operations we will later on be able to apply compiler consistency at  $\mathcal{IO}$ -points and lift the execution from the machine to the C-Level for an Multiprocessor ISA instantiation.

Now we will define the structure of our desired schedule. Taking computation  $\underline{C}$ , schedule  $\underline{\sigma}$  and external input sequence  $\underline{ext}$  we denote by the predicate  $\mathcal{IOsched}(\underline{C},\underline{\sigma},\underline{ext},n)$  that for the first  $n\in\mathbb{N}$  steps the computation exhibits a valid  $\mathcal{IO}$ -block schedule. For  $n\leq 1$  we have:

$$\mathcal{IO}sched(\underline{C}, \underline{\sigma}, \underline{ext}, 0) \equiv 1$$

$\mathcal{IO}sched(\underline{C}, \underline{\sigma}, \underline{ext}, 1) \equiv 1$

Each  $\mathcal{IO}$ -block schedule must start in an initial configuration with the first instruction of one machine. For n>1 the predicate is defined recursively as follows using the shorthand  $\mathcal{IO}_{\sigma^i}(C^i) \equiv \mathcal{IO}_{\sigma^i}(C^i,\sigma^i,in(C^i,\sigma^i,ext^i))$  for any computation  $\underline{C},\underline{\sigma},\underline{ext}$  and index i:

$$\begin{split} \mathcal{IO}sched( & \underline{C}, \, \underline{\sigma}, \underline{ext}, n ) \equiv \\ & \mathcal{IO}sched( \underline{C}, \, \underline{\sigma}, \underline{ext}, n-1 ) \wedge \\ & (\sigma^{n-1} \neq \sigma^{n-2} \Longrightarrow (\mathcal{IO}_{\sigma^{n-1}}(C^{n-1}) \vee \forall i < n-1. \, \sigma^i \neq \sigma^{n-1} ) ) \end{split}$$

This means an  $\mathcal{IO}$ -block schedule can be extended by adding a step of

- 1. the same currently running machine, or

- 2. another machine which

- (a) is currently at an  $\mathcal{IO}$ -point i.e., will be executing an  $\mathcal{IO}$  step, or

- (b) was never scheduled before.

Thus the schedule consists of blocks of steps by the same machine which start with an  $\mathcal{IO}$  step (or its first step) and are followed by instructions on the same machine which are not  $\mathcal{IO}$  steps.

# 4.2 Reordering Theorem

Every trace of steps in a multiprocessor system can be reordered into an equivalent  $\mathcal{IO}$ -block schedule independent of its safety with respect to the ownership model. We introduce the predicate  $safety(\underline{C}, \underline{\sigma}, \underline{ext}, n)$  which takes as inputs a CSO computation sequence  $\underline{C}$ , an arbitrary schedule  $\underline{\sigma}$  and an external input sequence  $\underline{ext}$ . It denotes the safety of all states that are reachable by n steps of the concurrent system.

$$\frac{C^0 \longrightarrow_{\Delta,\sigma,ext}^n C^n \quad inv(C^0) \quad \forall i < n. \ safe_{\sigma^i}(C^i)}{safety(\underline{C}, \, \underline{\sigma}, \, \underbrace{ext}, n)}$$

That means that the trace is safe iff its initial configuration  $C^0$  fulfills the ownership invariants and all steps from there leading into a configuration  $C^n$  are safe. For such safe traces we can construct a simulating trace of the same length which is an  $\mathcal{IO}$ -block schedule and also safe. Moreover we need to show that also for unsafe traces we are able to construct an unsafe  $\mathcal{IO}$ -block schedule starting in the same configuration.

When constructing equivalent  $\mathcal{IO}$ -block schedules it does not suffice to end up in the same configuration. We need to make sure that the new schedule is actually a reordering of the other. We capture this property and the relation between the reordered steps in the following judgement where we introduce

a permutation function  $u:\mathbb{N} \leftrightarrow \mathbb{N}$  which encodes the inverse reordering of machine steps thus yielding the original order. The shorthand  $in(C^i)$  replaces  $in(C^i,\sigma^i,ext^i)$  for any computation  $\underline{C},\underline{\sigma},\underline{ext}$  and index i.

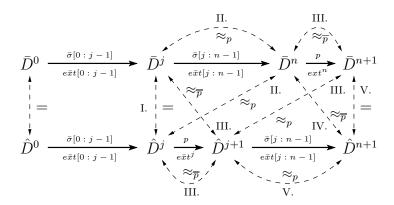

$$\begin{split} \hat{\sigma}^i &= \sigma^{u(i)} \quad \hat{C}^i \sim_{\hat{\sigma}^i} C^{u(i)} \quad \mathcal{IO}_{\hat{\sigma}^i}(\hat{C}^i) = \mathcal{IO}_{\sigma^{u(i)}}(C^{u(i)}) \\ \hat{C}^i &\sim_{\hat{\sigma}^i} C^{u(i)} \quad in(\hat{C}^i) \subseteq in(C^{u(i)}) \quad e\hat{x}t^i = ext^{u(i)} \\ \mathcal{IO}_{\hat{\sigma}^i}(\hat{C}^i) &\Longrightarrow \hat{C}^i &\stackrel{sv}{\sim} C^{u(i)} \land \hat{C}^i &\stackrel{\circ}{\sim} C^{u(i)} \land in(\hat{C}^i) = in(C^{u(i)}) \\ \hline & \qquad \qquad \underbrace{C}, \sigma, \underbrace{ext}, \hat{C}, \hat{\sigma}, \underbrace{ext}, i \vdash u \checkmark_{reord} \end{split}$$

Step i of the new schedule is part of a reordered schedule according to  $u^{-1}$  if the schedules are consistent and  $\mathcal{IO}$  steps are preserved. Moreover associated steps generally must be equivalent wrt. local components and ownership. For  $\mathcal{IO}$  operations we also require that the same shared and ownership state is visible and these steps must observe identical inputs in both traces. For local steps we only demand that there are no more inputs than in the original trace as non- $\mathcal{IO}$  steps do not react to their internal inputs anyway. External inputs however are observed identically in corresponding states.

In the following for clarity we abbreviate inputs to predicates of the form  $C, \sigma, ext$  by the first sequence (here: C) wherever this is possible. Assuming that a *Cosmos* model instantiation fulfills all parameter constraints we can now formulate our reordering theorem for  $\mathcal{IO}$ -block schedules, which justifies considering only such interleavings of machine steps. It consists of two parts.

## **Theorem 1** (*IO-Block Schedule Reordering*)

1. (Existence) For any safe Cosmos model computation  $\underline{C}$ ,  $\underline{\sigma}$ ,  $\underline{ext}$  which starts in a consistent state we can find a safe  $\mathcal{IO}$ -block schedule  $\underline{\hat{C}}$ ,  $\underline{\hat{\sigma}}$ ,  $\underline{ext}$  simulating the original one. The new schedule is a valid reordering of  $\underline{C}$ .

$$\forall \underline{C}, \underline{\sigma}, \underbrace{ext}, n \quad . \quad safety(\underline{C}, n)$$

$$\exists \underline{\hat{C}}, \underline{\hat{\sigma}}, \underbrace{e\hat{x}t}, u \quad . \quad \bigwedge \left\{ \begin{aligned} safety(\underline{\hat{C}}, n), & \mathcal{IO}sched(\underline{\hat{C}}, n), \\ \hat{C}^0 &= C^0, & \hat{C}^n &= C^n, \\ \forall i < n. \ \underline{C}, \underline{\hat{C}}, i \vdash u \sqrt{reord} \end{aligned} \right\}$$

2. (Soundness) For any unsafe schedule we can find an unsafe IO-block schedule which starts in the same initial configuration.

$$\begin{split} &\forall \underline{C}, \underbrace{\sigma}, \underbrace{ext}, n \quad . \quad C^0 \longrightarrow_{\Delta,\sigma,ext}^n C^n \wedge / safety(\underline{C}, n) \\ \\ \exists \underline{\hat{C}}, \underline{\hat{\sigma}}, \underbrace{e\hat{x}t}, \hat{n} \leq n \quad . \quad & \bigwedge \left\{ \begin{aligned} \hat{C}^0 \longrightarrow_{\Delta,\hat{\sigma},e\hat{x}t}^{\hat{n}} \hat{C}^{\hat{n}}, & \hat{C}^0 = C^0, \\ / safety(\underline{\hat{C}}, \hat{n}), & \mathcal{IO}sched(\underline{\hat{C}}, \hat{n}) \end{aligned} \right\} \end{split}$$

An illustrating example of the reordering can be found in Figure 1. The external inputs can be interpreted as external interrupts which are triggered by a device or interrupt controller and handled by processor machines 2 and 3. The grey boxes represent  $\mathcal{IO}$  steps which keep their order. Local steps of some machine

Figure 1: Example for reordering an arbitrary *Cosmos* model schedule  $\underline{\sigma}$ ,  $\underline{ext}$  into an  $\mathcal{IO}$ -block schedule  $\underline{\hat{\sigma}}$ ,  $\underline{ext}$  with np=4; boxes marked with 0 to 3 are steps of machines with the respective identifier; greyish steps are representing  $\mathcal{IO}$  steps; lightnings denote reactions to external inputs;  $I_2$  and  $I_3$  are singleton sets containing input signals handled only by machine 2 and 3 respectively; arrows illustrate the reordering of  $\mathcal{IO}$  steps

p can be reordered across steps of other machines. Nevertheless the order in which p executes them is preserved.

Note also that in the figure it appears that external inputs obey the common external interrupt convention which states that interrupt signals should be stable until they are acknowledged by the receiver. We maintained this convention in both schedules  $\underline{\sigma}$  and  $\hat{\underline{\sigma}}$  for the steps where the respective receiving machines where not scheduled. As we mentioned before external inputs for machine p in  $\underline{ext}$  at step i are redundant when  $\sigma^i \neq p$  and we can actually omit them. However in the example we kept active the inputs for 2, and 3 respectively, also during steps of other machines in order to keep the picture simple and convey the actual continuity of the input in a real application where all machines are truly running in parallel. In a concurrent system with a scheduling function there is only an abstract notion of timing for inputs and interrupts, tied to the steps of machines reacting to them. This connection between machine steps and external inputs wrt.  $\underline{C}$  and  $\hat{\underline{C}}$  is formulated in  $u\sqrt{r_{eord}}$ .

Observe that we do not need the valid reordering property for soundness. In our setting *Cosmos* model executions must be safe for all schedules and external input sequences, hence it is sufficient to find an arbitrary unsafe  $\mathcal{IO}$ -block schedule starting in the same configuration to guarantee soundness. We believe that our formulation of this order reduction theorem is correct and usable. For demonstration in Section 4.5 we will show how to apply it in a system verification task and transfer safety and verified program properties from  $\mathcal{IO}$ -Block schedules to arbitrary ones. Before we give the proof of the theorem we have to introduce some helpful notation and lemmata.

# 4.3 Auxilliary Definitions and Lemmata

In order to prove the theorem we split the equality between CSO configurations into two subrelations  $\approx_p$  and  $\approx_{\overline{p}}$  which distinguish the machine-local and the global state wrt. some machine p. Based on these relations we introduce helpful lemmata which we will use in the reordering proof later on. Firstly we define the two equivalence relations  $\approx_p$  and  $\approx_{\overline{p}}$  on the set of *Cosmos* model configurations taking into account the memory contents of the ownership domain and the register values of a certain machine p < np.

$$\begin{array}{lcl} C \approx_p C' & \equiv & C \sim_p C' \wedge C \stackrel{o}{\sim}_p C' \\ C \approx_{\overline{p}} C' & \equiv & \forall p' \neq p. \ C \sim_{p'} C' \wedge C \stackrel{sv}{\sim} C' \wedge \mathcal{O}_p = \mathcal{O}_p' \end{array}$$

The relations shall imply that from equivalent configurations a machine p will take the same local step for  $\approx_p$ , or any other machine than p will take the same step for  $\approx_{\overline{p}}$  respectively. Below we make some useful observations.

**Corollary 2** *From the definitions it directly follows for any*  $p \in \mathbb{N}_{np}$  *that*

- 1.  $C \approx_p C' \wedge C \approx_{\overline{p}} C'$  is equivalent to C = C'.

- 2.  $C \approx_{\overline{p}} C'$  implies  $C \approx_{p'} C'$  for all  $p' \neq p$ .

- 3.  $C \approx_{\overline{n}} C'$  implies  $C \stackrel{o}{\sim} C'$ .

- 4.  $C \approx_{\overline{p}} C'$  and  $\omega_p(C) = \omega_p(C')$  implies in(C, p', ext) = in(C', p', ext) due to  $constr_{\omega}(p')$  for all  $p' \in \mathbb{N}_{np}$  and  $ext \subseteq \mathfrak{E}$ .

- 5.  $C \approx_p C'$  and  $C \stackrel{sv}{\sim} C'$  implies  $C \sim_p^A C'$  for the set  $A = \mathcal{O}_p \cup C.\mathcal{S} \cup \mathcal{R}$ .

Assuming the parameter constraint we can prove the following lemmata for our relations  $\approx_p$  and  $\approx_{\overline{p}}$ .

**Lemma 2** The relations  $C \approx_p C'$  and  $C \approx_{\overline{p}} C'$  are equivalence relations for any machine  $p \in \mathbb{N}_{np}$ .

PROOF: Obviously  $C \sim_p C'$  is reflexive. Moreover it is symmetric and transitive in conjunction with  $\mathcal{O}_p = \mathcal{O}'_p$  which is guaranteed by  $C \stackrel{\circ}{\sim}_p C'$ . The latter is an equivalence relation because it only uses unquantified equalities in its definition. Hence  $C \approx_p C'$  is an equivalence relation as well.  $C \approx_{\overline{p}} C'$  is an equivalence relation because its definition is based exclusively on equalities,  $C \stackrel{\circ}{\sim}_p C'$  and the equivalence relation  $\stackrel{v}{\sim}_p$ .

We need a lemma on the safety of steps in equivalent *Cosmos* configurations.