# Balancing the Load

Leveraging a Semantics Stack for Systems Verification

Eyad Alkassar · Mark A. Hillebrand · Dirk C. Leinenbach · Norbert W. Schirmer · Artem Starostin · Alexandra Tsyban

Received: date / Accepted: date

Abstract We have developed a stack of semantics for a high-level C-like language and low-level assembly code, which has been carefully crafted to support the pervasive verification of system software. It can handle mixed-language implementations and concurrently operating devices, and permits the transferral of properties to the target architecture while obeying its resource restrictions. We demonstrate the applicability of our framework by proving the correct virtualization of user memory in our microkernel, which implements demand paging. This verification target is of particular interest because it has a relatively simple top-level specification and it exercises all parts of our semantics stack. At the bottom level a disk driver written in assembly implements page transfers via a swap disk. A page-fault handler written in C uses the driver to implement the paging algorithm. It guarantees that a step of the currently executing user can be simulated at the architecture level. Besides the mere theoretical and technical difficulties the project also bore the social challenge to manage the large verification effort, spread over many sites and people, concurrently contributing to and maintaining a common theory corpus. We share our experiences and elaborate on lessons learned.

$\textbf{Keywords} \ \ \text{Pervasive formal verification} \cdot \text{systems verification} \cdot \text{software verification}$

### 1 Introduction

The context of this work is the German Verisoft project, a large scale effort bringing together industrial and academic partners to push the state of the art in formal verifi-

Work supported by the German Federal Ministry of Education and Research (BMBF) under grant 01 IS C38. Work of the first and the third author supported by DFG Graduiertenkolleg "Leistungsgarantien für Rechnersysteme". Work of the fifth author supported by the International Max Planck Research School for Computer Science (IMPRS-CS).

M. A. Hillebrand · D. C. Leinenbach · N. W. Schirmer

German Research Center for Artificial Intelligence (DFKI), P.O. Box 15 11 50, 66041 Saarbrücken, Germany

E-mail: {mah, Dirk.Leinenbach, Norbert.Schirmer}@dfki.de

E. Alkassar · A. Starostin · A. Tsyban

Saarland University, Computer Science Dept., P.O. Box 15 11 50, 66041 Saarbrücken, Germany E-mail: {eyad, starostin, azul}@wjpserver.cs.uni-sb.de

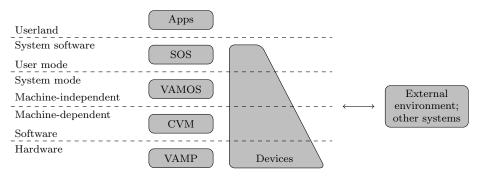

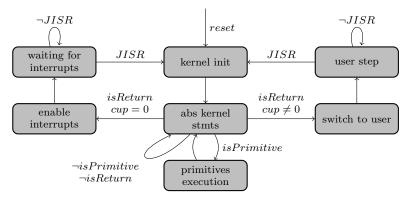

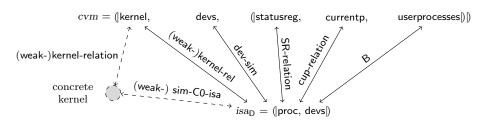

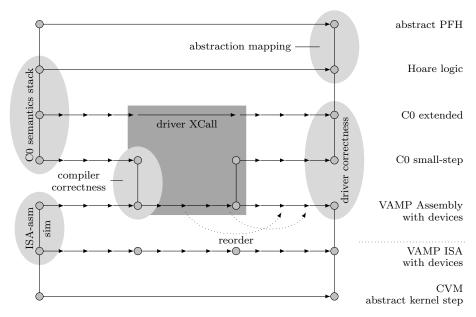

Fig. 1 Implementation layers of the academic system (Verisoft subproject 2)

cation for realistic computer systems, comprising hard- and software. In this article we present parts of Verisoft's 'academic system', which is a computer system for writing, signing, and sending emails. As it covers all implementation layers from the gate level hardware up to communicating user processes it is a representative of a vertical slice of a general-purpose computer system. We pay special attention to pervasive verification, which means that at the end of the day we obtain a correctness result for the actual system, which is the hardware running the system. We do not only verify isolated portions on different abstraction layers but make sure that we can combine and preserve the results for the actual system.

One key obstacle in a large formal and layered artefact as the Isabelle/HOL theories of our project is the seamless integration of the abstraction layers. This is achieved through simulation and transfer theorems, gluing together the layers. The results presented in conference articles are often simplified since they focus on a certain point and have to fit into the page limit. With this article we attempt to overcome a popular demand and present key theorems of the Verisoft system stack up to the microkernel level in great detail. We do not present all the underlying definitions. Here we refer to previous work and our repository. Instead we discuss the shape of the theorems and the nature of various assumptions with regard to their role in the overall verification.

System stack. The hardware architecture is called VAMP, a DLX like processor that supports address translation and memory-mapped I/O devices. With the next level of communicating virtual machines (CVM) a hardware-independent programming interface for a microkernel is provided, that establishes the notion of separate concurrent user processes. Parts of the CVM are implemented in assembly, because C0, our main implementation language and a subset of C, lacks some low-level programming constructs. On the basis of the CVM our microkernel VAMOS [DDB08] is programmed in pure C0. The simple operating system (SOS) is implemented as a (privileged) user process of VAMOS [Bog08]. It offers file I/O, network access and inter-process communication. On top of it user applications are provided with a client / server architecture based on remote procedure calls [ABP09]. Finally these user applications implement the functionality of the academic system: signing software, SMTP client and server [LNRS07], and a simple mail user agent [BHW06]. The implementation stack is also depicted in Figure 1.

$<sup>^1\,</sup>$  The Isabelle theories of all models and proofs of this article are available in the published portions of the Verisoft repository [HP08] at http://www.verisoft.de/VerisoftRepository.html.

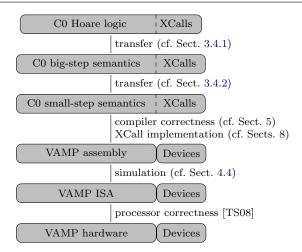

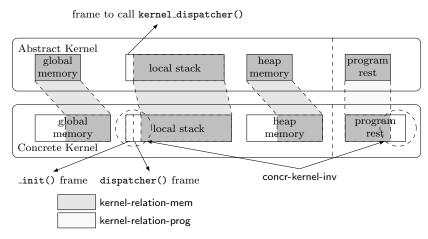

Fig. 2 Semantics stack

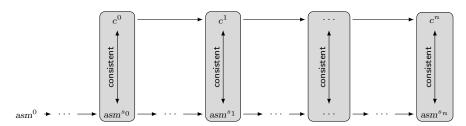

The computational models we introduce to specify and verify the academic system are assembled along the implementation layers. In this article we focus on the layers up to the CVM, where the challenging aspect is the integration of concurrent computations of the processor and devices at the architecture level into the sequential view provided by the C0 (and assembly) language. We introduce the C0 semantics stack which is orthogonal to the system stack described before. With the semantics stack we establish a convenient Hoare logic to reason about the sequential parts of C0 programs (without inline assembly code) and simultaneously provide the means to compose the results to deal with assembly code and to integrate devices.

Semantics stack. The C0 semantics stack comprises a Hoare logic, a big-step semantics, and a small-step semantics. It can be continued to the VAMP machine level, which is divided further into assembly layer, instruction set architecture, and gate level hardware. An overview is depicted in Figure 2. By a higher level of abstraction in the Hoare logic compared to the small-step semantics, we gain efficiency for the verification of individual C0 programs. However, since the semantics stack is merely a proof device for C0 programs we have to integrate the results obtained in the Hoare logic to our systems stack. We supply soundness and simulation theorems that permit the transferral of program properties from the Hoare logic down to the small-step semantics. Applying compiler correctness we map those properties to assembly machines. We can get further down to the ISA layer by employing a simulation theorem and finally to the hardware by employing a processor correctness result.

The Hoare logic provides sufficient means to reason about pre and postconditions of sequential, type-safe, and assembly-free C0 programs. Compiler correctness, though, is formulated at the small-step semantics level. This allows the integration with inline assembly code or concurrent computations, e.g., introduced by devices. The big-step semantics is a bridging layer, which is convenient to express the results of the Hoare logic operationally. The differences reflect the purpose of the layers. The Hoare logic is tuned to support verification of individual programs, whereas the small-step semantics is better suited for arguments about interleaving programs at the system level.

Up to now we have argued how to bring the results down to the lower levels such that we can conduct reasoning at a comfortable abstraction level. However, this comes at the cost of expressiveness. Most prominently only the levels below C0 allow the integration of devices, which are a concurrent source of computation. As soon as we attempt to reason about C0 programs that use these devices we either have to be able to express device operations at the Hoare logic level or we are forced to carry out the whole verification at the assembly level. Our approach is to abstract the effect of those low-level computations into atomic 'XCalls' (extended calls) in all our semantic layers. The state space of C0 is augmented with an additional component that represents the state of the external component, e.g., the device. An XCall is a procedure call that makes a transition on this external state and communicates with C0 via parameter passing and return values. With this model it is straightforward to integrate XCalls into the semantics and into Hoare logic reasoning. The XCall is typically implemented in assembly. An implementation proof of this piece of assembly justifies the abstraction to an atomic XCall.

Somewhat similar to the XCalls in the C0 semantics layers, devices are added to all the semantic layers of the VAMP. Their state and transition functions are shared between all layers. These transition functions as well as the VAMP semantics describe small-step computations, which are interleaved to obtain the concurrent computation of the combined system. One central prerequisite to use our individual transfer results to prove a global property for the combined system is to disentangle the different computations by means of reordering.

Related work. As Klein [Kle09] provides an excellent and comprehensive overview of the history and current state of the art in operating systems verification we limit this paragraph to highlight the peculiarities of our work. We extend the seminal work on the CLI stack [BHMY89] by integrating devices into our model and targeting a more realistic system architecture regarding both hard and software. The project L4.verified [HEK<sup>+</sup>07] focuses on the verification of an efficient microkernel, rather than on formal pervasiveness, as no compiler correctness or an accurate device interaction is considered. In the FLINT project, an assembly code verification framework is developed and code for context switching on a x86 architecture was formally proven [NYS07]. A program logic for assembly code is presented, but no integration of results into highlevel programming languages is undertaken. Relevant references to our own work are given at the beginning of each section.

Outline. In Section 2 we introduce Isabelle/HOL and notational conventions. In Section 3 we introduce the language C0 and the associated semantics stack. We present theorems that permit the transferral of properties from the Hoare logic down to the small-step semantics. In Section 4 we present models for the assembly language and instruction set of the VAMP architecture. We also show how to integrate devices into these models. Section 5 deals with verified compilation from C0 to VAMP. In Sections 6 to 8 previous results are employed and combined to establish a correctness result for CVM. Going top-down we first present the theorem for CVM user step correctness in Section 6. One case in the proof of this theorem is the correct handling of page-faults. In Section 7 we present the page-fault handler that implements demand paging for CVM. For paging operations it uses a disk driver, which is presented in Section 8. We wrap up our experience and 'lessons learned' in Section 9. In the appendix we provide a glossary on important constants and notations.

#### 2 Preliminaries

The formalizations presented in this article are mechanized and checked within the generic interactive theorem prover *Isabelle* [Pau94]. Isabelle is called generic as it provides a framework to formalize various *object logics* that are declared via natural deduction style inference rules within Isabelle's meta-logic *Pure*. The object logic that we employ for our formalization is the higher order logic of *Isabelle/HOL* [NPW02].

This article is written using Isabelle's document generation facilities, which guarantees that the presented theorems correspond to formally proven ones. We distinguish formal entities typographically from other text. We use a sans serif font for types and constants (including functions and predicates), e.g.,  $\mathsf{map}$ , a slanted serif font for free variables, e.g., x, and a slanted sans serif font for bound variables, e.g., x. Small capitals are used for data type constructors, e.g., FOO, and type variables have a leading tick, e.g., 'a. HOL keywords are typeset in type-writer font, e.g.,  $\mathsf{let}$ . We also take the freedom to borrow C notation, e.g.,  $\mathsf{unsigned}$  when presenting CO.

As Isabelle's inference kernel manipulates rules and theorems at the Pure level the meta-logic becomes visible to the user and also in this article when we present theorems and lemmas. The Pure logic itself is intuitionistic higher order logic, where universal quantification is  $\bigwedge$  and implication is  $\Longrightarrow$ . Nested implications like  $P_1 \Longrightarrow P_2 \Longrightarrow P_3 \Longrightarrow C$  are abbreviated with  $[P_1; P_2; P_3] \Longrightarrow C$ , where one refers to  $P_1, P_2$ , and  $P_3$  as the premises and to C as the conclusion. To group common premises and to support modular reasoning Isabelle provides locales [Bal03, Bal06].

In the object logic HOL universal quantification is  $\forall$  and implication is  $\longrightarrow$ . The other logical and mathematical notions follow the standard notational conventions with a bias towards functional programming. We only present the more unconventional parts here. We prefer curried function application, e.g., f a b instead of f(a, b). In this setting the latter becomes a function application to *one* argument, which happens to be a pair.

Isabelle/HOL provides a library of standard types like Booleans, natural numbers, integers, total functions, pairs, lists, and sets and packages to define new data types and records. Isabelle allows polymorphic types, e.g., 'a list is the list type with type variable 'a. In HOL all functions are total, e.g.,  $\mathtt{nat} \Rightarrow \mathtt{nat}$  is a total function on natural numbers. Function update is  $f(y := v) \equiv \lambda x$ . if x = y then v else f(x) and function composition is f(x) = y. To formalize partial functions the type 'a option is used. It is a data type with two constructors, one to inject values of the base type, e.g., [x], and the additional element [x]. A base value can be projected with the function the, which is defined by the sole equation the [x] = x. Since HOL is a total logic the term the [x] is still a well-defined yet un(der)specified value. Partial functions can be represented by the type 'a [x] option, abbreviated as 'a [x] 'b.

The syntax and the operations for lists are similar to functional programming languages like ML or Haskell. The empty list is [], with  $x \cdot xs$  the element x is 'consed' to the list xs, the head of list xs is hd xs and the remainder, its tail, is tl xs. With xs @ ys list ys is appended to list xs. With map f xs the function f is applied to all elements in xs. The length of a list is |xs|, the n-th element of a list can be selected with xs[n] and updated via xs[n:=v]. An entry of a two-dimensional list is updated by xs[n, m:=v]. With set xs we obtain the set of elements in list xs. Filtering those elements from a list for which predicate P holds is achieved by  $[x \in xs \cdot P \ x]$ . With replicate n e we denote a list that consists of n elements e.

**Table 1** C0 Expressions e

Lit v literal values vVarAcc vn access of variable vnARRACC  $e_{\mathsf{a}}$  eindexing array  $e_{\mathsf{a}}$  with index eStruct $Acc\ e\ cn$ selecting component cn of structure eBINOP bop e<sub>1</sub> e<sub>2</sub> binary operation LAZYBINOP lbop e<sub>1</sub> e<sub>2</sub> lazy binary operation Unop uop e unary operation Addrof eaddress of (left-) expression e Deref edereferencing e

Sets come along with the standard operations for union, i.e.,  $A \cup B$ , intersection, i.e.,  $A \cap B$  and membership, i.e.,  $x \in A$ . The set image f ' A yields a new set by applying function f to every element in set A.

Partial functions  $a \rightharpoonup b$  are commonly used as maps. With map-of xs we construct a map from an association list, i.e., a list of key / value pairs. We denote the domain of map m by dom m. With  $m_1 ++ m_2$  we add the map  $m_2$  to map  $m_1$ , where entries of  $m_1$  are overwritten if necessary. We can restrict the domain of a map m to a set  $m_1 = m_2 = m_1 = m_2$  by  $m_1 = m_1 = m_2 = m_2$

A record is constructed by assigning all of its fields, e.g.,  $(fld_1 = v_1, fld_2 = v_2)$ . Field  $fld_1$  of record r is selected by  $r.fld_1$  and updated with a value x via  $r(fld_1 := x)$ .

The first and second component of a pair can be accessed with the functions fst and snd. Tuples with more than two components are pairs nested to the right.

#### 3 C0

C0 is a type safe subset of C designed with verification in mind. An elaborate description of the big-step semantics is given in [Sch06] and the small-step semantics is introduced in [Lei08]. An overview on the simulation theorems between the semantical layers can be found in [AHL $^+$ 08], the transfer from the Hoare logic to the big-step semantics is detailed in [Sch06].

The primitive values are signed and unsigned integers (32 bit), 8-bit chars, Booleans, and typed pointers. Aggregate values comprise structures and arrays. Unions and pointer arithmetic are not supported. C0 Expressions e and statements s are defined as data types (cf. Tables 1 and 2). Binary operations are arithmetic operations (+, -, \*, /, %), bitwise operations (|, &, ^, <<, >>), and comparisons (>, <, ==, !=, >=, <=). Lazy binary operations are Boolean conjunction && and disjunction ||. Unary operations are unary minus -, bitwise negation ^, logical negation !, and operations to convert between integral values (integers, unsigned integers, and chars). Left expressions are the subset of expressions that refer to memory objects (e.g., VARACC, ARRACC, STRUCTACC, and DEREF).

Statement identifiers *sid* are used in the compiler correctness theorem. Procedures assign the return value to a (global or local) variable specified by variable name *vn*. External procedure calls (ESCALL) are stubs for a linker that eventually replaces them by ordinary procedure calls. Extended procedures (XCALL) can return multiple values to a list of left-expressions. This is the only way for an XCall to manipulate the ordinary

#### Table 2 C0 Statements s

$\begin{array}{lll} \text{SKIP} & \text{the empty statement} \\ \text{COMP } s_1 \ s_2 & \text{sequential composition} \end{array}$

Assign  $e_l$  e sid assignment of expression e to left-expression  $e_l$  PALLOC  $e_l$  tn sid allocation of object of type name tn and assignment to

pointer e

SCALL vn pn es sid procedure call of pn with parameters es and result vn

RETURN  $e \, sid$  return from procedure IFTE  $e \, s_1 \, s_2 \, sid$  if-then-else with condition e

LOOP e s sid while loop with condition e and body s Asm ls sid inline assembly with instruction list ls

ESCALL vn pn es sid external procedure call

XCALL pn es es, sid extended procedure call of pn with parameters es and

result left-expressions es<sub>r</sub>

C0 state, since it only operates on the extended state directly. Multiple return values nevertheless allow us to model updates to global variables or heap updates via pointers.

The extended state component on which XCalls operate is the same for all semantic layers. An extended procedure is defined semantically as a function that takes a list of parameter values and an extended state component and returns the new extended state component and a list of result values. This definition is then consulted to perform an XCall. Evaluating parameter expressions and returning the result values is handled by the C0 semantics itself. It depends on the semantical layer how the parameter and result values are represented. The small-step semantics flattens aggregate values to a list of bytes, whereas the big-step semantics and Hoare logic keep them together. Nevertheless, the definitions of the extended procedure definitions on the different layers have a lot in common since the core part is the transition on the extended state component. This makes the transfer of those definitions between the layers straightforward.

The different C0 semantics do not handle all statements. Neither of the C0 semantics handle assembly statements ASM, which are only meaningful in the assembly machines. We deal with C0 programs with inline assembly code by combining the C0 small-step semantics and the assembly semantics, both of which are tied together via compiler correctness. The small-step semantics describes the computation of the C0 program up to the point where an assembly statement is reached. The compiler correctness theorem allows us to relate the C0 small-step configuration to the assembly machine, which can then continue computation of the assembly parts. If the assembly part does not destroy any of the C0 invariants, the final assembly configuration can be mapped back to a C0 configuration from which the C0 computation can continue.

Furthermore, the Hoare logic and the big-step semantics do not support ADDROF expressions. This simplifies the memory model for global and local variables.

Regarding initialization of memory, C0 is quite strict. Heap memory is initialized by the (implementation of the) PALLOC statement. Global variables are initialized by the compiler. For local variables we employ a *definite assignment* analysis, which statically ensures that we only read from variables that were previously assigned to.

## Definition 1 (Definite assignment analysis) The analysis has two parts:

$\mathcal{A}$  s: is the set of variables that are guaranteed to be assigned to by any execution of statement s.

$\mathcal{D}$  s L A: means that statement s passes the definite assignment check, with respect to the set of local variables L and the initially assigned variables A.

The analysis A s collects assignments to local as well as global variables. That is why this set is often intersected with the local variables L.

The typing constraints on C0 programs are not only employed for static typing, but are also used as typing invariants during execution of a statement. Hence they do not solely depend on static information but also on the dynamic configuration, e.g., to determine the type of a heap location. Since configurations are different for the big-step and the small-step semantics we postpone the definitions until Sections 3.2 and 3.3.

The core differences of the semantical layers of C0, which we introduce in the following sections, can be summarized as follows:

Hoare: split heap, aggregate values, implicit typing Big-step: single monolithic heap, aggregate values, explicit typing Small-step: single monolithic heap, flat values, explicit typing

These design decisions reflect the purpose of the layers. The Hoare logic is tuned to support verification of individual programs, whereas the small-step semantics is better suited for arguments about interleaving programs at the system level. C0 supports aggregate values, i.e., structures and arrays. As in hardware those values are broken down to a sequence of bytes in the small-step semantics. This allows us to calculate addresses of subcomponents in memory. At the big-step and the Hoare-level however, those aggregate values are stored in one 'memory cell'. One can still assign to subcomponents via ordinary left-expressions, but one cannot calculate the address of a subcomponent. The 'address-of' operator is not supported at the big-step and Hoare level. This rules out aliasing between different types and structure components. We exploit this guarantee by using a split heap memory model in the Hoare logic. Every component of a structure is stored in a separate heap [Bur72]. An assignment to one component does not affect any other components (of the same structure or other structures), which simplifies program verification. Type safety of C0 guarantees that this model can be mapped to the single monolithic heap of the other semantic layers.

Since we do not need a general theory of the C0 language at the Hoare logic level, we take the freedom to supply an individual state space for each program we verify. Every variable (and every split heap) becomes a field in a state space record, with its own HOL type. We employ the HOL type system to model C0 programming language types. Isabelle's type inference then takes care of typing constraints that would otherwise have to be explicitly maintained in the assertions. Again, type safety of C0 is the reason that allows us to connect the Hoare logic layer with the big-step semantics.

## 3.1 Hoare logic

The Hoare logic layer is somehow special compared to the big-step and small-step layer, since it is not C0 specific. It uses a general framework for the verification of sequential imperative programs within Isabelle/HOL [Sch05,Sch06]. The language model is called Simpl, and we embed C0 into it. The framework comes along with syntax, big- and small-step semantics, Hoare logics for partial as well as total correctness and an automated verification condition generator for Simpl. Soundness and completeness of the Hoare logic with respect to the operational semantics of Simpl is proven. We use the soundness theorem to transfer a Hoare triple about a C0 program to the operational semantics of Simpl. A correctness theorem about our embedding of C0 into Simpl then allows us to map these results to the big-step semantics of C0 [AHL<sup>+</sup>08].

Since Simpl is generic it does not stipulate the representation of the state space, which is just a type variable. For our C0 instantiation we use a HOL record as state space, that we construct for a given program. The basic notions we need are big-step execution and guaranteed termination of Simpl programs.

**Definition 2 (Big-step execution for Simpl)** The judgment  $\Gamma \vdash_h \langle s, \sigma \rangle \Rightarrow \tau$  means that in context of program  $\Gamma$  the statement s started in initial state  $\sigma$  executes to the final state  $\tau$ , where  $\Gamma$  maps procedure names to their bodies and  $\sigma$  and  $\tau$  are states of the form NORMAL  $\sigma'$  or FAULT f, where f is an error flag.

**Definition 3 (Guaranteed termination for Simpl)** The judgment  $\Gamma \vdash_h s \downarrow \sigma$  means that in context of program  $\Gamma$  execution of statement s from initial state  $\sigma$  is guaranteed to terminate.

In this article we are concerned with total correctness properties of the form  $\Gamma \models_h P \ s \ Q$ . Starting in a state that satisfies the precondition, execution of the statement is guaranteed to terminate without error and the final state satisfies the postcondition.

## Definition 4 (Total correctness for Simpl)

```

\Gamma \models_{\mathsf{h}} P \ s \ Q \equiv \forall \ \sigma \in \text{Normal '} P. \ \Gamma \vdash_{\mathsf{h}} s \downarrow \sigma \land (\forall \ \tau. \ \Gamma \vdash_{\mathsf{h}} \langle s, \ \sigma \rangle \Rightarrow \tau \longrightarrow \tau \in \text{Normal '} Q)

```

#### 3.2 Big-step semantics

A state  $\sigma$  in the big-step semantics is parametrized over the state extension 'x and is a record with the following components: the heap  $\sigma$ -heap maps locations to values, local variables  $\sigma$ -lcls and global variables  $\sigma$ -glbs map variable names to values, the natural number  $\sigma$ -free-heap indicates the available heap memory, and  $\sigma$ -ext is placeholder of type 'x for the extended state for XCalls.

A program  $\Pi$  is a four-tuple containing association lists for the various declarations of types, global variables, procedures, and extended procedures (for XCalls). We access this declaration information via the following functions: tnenv  $\Pi$  to resolve type names, genv  $\Pi$  to obtain type information for global variables, plookup  $\Pi$  and xplookup  $\Pi$  to lookup the definitions of procedures and XCalls.

**Definition 5 (Big-step execution for C0)** Judgment  $\Pi, sz, L \vdash_{bs} \langle s, \sigma \rangle \Rightarrow \tau$  means, that in context of program  $\Pi$ , the size function sz (to measure heap memory consumption of a type), and the set of local variables L, execution of the statement s in initial state  $\sigma$  leads to the final state  $\tau$ .

The states  $\sigma$  and  $\tau$  are of the form  $\lfloor \sigma' \rfloor$  in case of normal execution or  $\bot$  if an error occurred. The set of local variable names L is used to disambiguate accesses to local or global variables (local names hide global names). It is set to the local variables during a procedure call, whereas program  $\Pi$  and size function sz stay the same during the whole execution.

The size function sz is considered when allocating new heap memory. If enough memory is available a new object is created otherwise we nondeterministically return the null pointer or create a new object. We keep the size function as a parameter of the execution relation to gain some flexibility in when to discharge resource limitations. It shows up in variations also in the small-step semantics and in the compiler correctness theorem (cf. Sections 3.3 and 5.2) where it finally has to be discharged. If we choose to

take a trivial size function (i.e., one that is constantly 0) we have to argue harder about memory restrictions later. Using a more appropriate size function allows us to carry out reasoning about memory restrictions already at the Hoare logic level (cf. Page 18).

Typing. The typing judgment for statements takes the static declaration information of the program into account. Moreover, as we also use typing to describe execution invariants it considers a heap typing HT, which maps locations to type names. In the big-step semantics the type information of heap locations is not maintained in the heap. This is not necessary for the execution of a C0 program since there is no runtime type information. For expressing type safety however we need this type information and introduce it via the heap typing.

**Definition 6 (Typing of a statement)** Judgment  $xpt, pt, tt, VT, HT \vdash_{bs} s \sqrt{expresses}$  that statement s is well-typed with respect to the extended procedure table xpt, procedure table pt, type table tt, variable typing VT, and the heap typing HT.

For a given program  $\Pi$  usually tt is obtained by thenv  $\Pi$ , pt by plookup  $\Pi$ , and so forth. The variable typing VT is typically constructed by overwriting the global variable environment genv  $\Pi$  with the active local variable environment.

As a statement has to be well-typed the memories have to conform to the typing information. First we introduce a typing judgment for values, which we then extend to memories, by ensuring that every value is typed according to a memory typing MT.

**Definition 7 (Typing of a value)** The judgment  $HT,tt \vdash_{bs} v::_{v}T$  means that value v has type T in the context of heap typing HT and type table tt.

## Definition 8 (Typing of memory)

```

HT,tt\vdash_{\mathsf{bs}} m::MT \equiv \forall \ \textit{p} \ \textit{v} \ T. \ m \ \textit{p} = |\ \textit{v}\ | \ \land \ MT \ \textit{p} = |\ \textit{T}\ | \longrightarrow HT,tt\vdash_{\mathsf{bs}} \textit{v}::_{\mathsf{v}} T

```

Finally, we extend well-typedness to complete states. Local and global variables as well as the heap have to respect typing. For the heap, type information is obtained by composition of the type table  $t\bar{t}$  and the heap typing HT. For global variables and the heap we additionally demand that at least as much locations or variables are initialized as in the typings. Global variables are always initialized and typing GT is constant during program execution. The heap typing HT gets extended as new objects are allocated. The number of allocated locations stays finite during execution. Local variables do not have to be initialized from the beginning of the procedure. However, the definite assignment analysis ensures that we only read initialized variables. In the invariants we use restricted local typings LT that correspond to the approximation of the definite assignment analysis.

## Definition 9 (Typing of state)

```

tt\vdash_{\mathsf{bs}}\sigma::HT,LT,GT\equiv HT,tt\vdash_{\mathsf{bs}}\sigma.\mathsf{heap}::(tt\circ_{\mathsf{m}}HT)\wedge\mathsf{dom}\;HT\subseteq\mathsf{dom}\;\sigma.\mathsf{heap}\;\wedge\\\mathsf{finite}\;(\mathsf{dom}\;\sigma.\mathsf{heap})\wedge HT,tt\vdash_{\mathsf{bs}}\sigma.\mathsf{lcls}::LT\wedge HT,tt\vdash_{\mathsf{bs}}\sigma.\mathsf{glbs}::GT\wedge\mathsf{dom}\;GT\subseteq\mathsf{dom}\;\sigma.\mathsf{glbs}

```

**Definition 10 (Valid programs)** We define the predicate valid-prog  $\Pi$  to ensure basic well-formedness and typing properties for programs. In particular we require:

- identifiers within the different name spaces of type names, global variable names, local variable names, procedure names and extended procedure names are unique,

- every procedure body is well-typed and passes the definite assignment check, and

- $-\,$  the semantic definitions of the extended procedures respect their signature.

#### 3.3 Small-step semantics

In contrast to a big-step semantics that only relates the initial to the final state of a statement execution, a small-step semantics describes single computation steps operating on configurations. A configuration c is a record with two components: the memory c.mem and the program rest c.prog, which is a C0 statement. The memory configuration is a record with three components: the memory for global variables c.mem.gm, the heap memory c.mem.hm, and the frame stack c.mem.lm. Each frame is a pair containing the memory of local variables and the destination for the return value.

A memory m not only contains the values but also type and initialization information: the word addressable memory content  $m.\mathsf{ct}$ , a symbol table  $m.\mathsf{st}$  associating variable names to types, and the set  $m.\mathsf{init\text{-}vars}$  of initialized variables. Single memory cells of the small-step semantics are represented as an abstract data type and can store a single value of basic type. We have a constructor for every basic type, e.g.,  $\mathsf{unsigned}$  n for storing unsigned value n in a memory cell. In case of the heap memory the set of initialized variables and the variable names in the symbol table are meaningless, but the type information describes the objects in the heap.

We introduce a record for monolithic C0 small-step configurations  $c_{\mathsf{m}}$  combining a small-step configuration  $c_{\mathsf{m}}.\mathsf{conf}$ , a type table  $c_{\mathsf{m}}.\mathsf{tt}$  and a procedure table  $c_{\mathsf{m}}.\mathsf{pt}$ .

We refer to the memory objects of a C0 small-step configuration by the term generalized variables (or short: g-variable). This also includes all heap objects. Formally, g-variables are represented as a data type, e.g., GVAR-HM i for the i-th heap variable or GVAR-ARR g i for the i-th array element of g-variable g. Pointers are null (NULL) or point to a g-variable (PTR g).

**Definition 11 (Transition function \delta)** The small-step transition function  $\delta$  tt pt enough-heap c gets the type table tt, the procedure table pt, and the predicate enough-heap which takes the memory and a type as parameter and decides whether the allocation of a new object of that type succeeds. For property transfer between the big-step and the small-step semantics this has to be compatible with the sz function used there. If no fault occurs the result of the transition from the old configuration c is of the form |c'|, otherwise it is the error configuration  $\bot$ . We execute n steps by  $\delta^n$ .

The transition function  $\delta$  describes the C0 source level semantics of the compiler correctness theorem. It does not properly handle XCalls but returns a final configuration (where the program rest is SKIP). Hence, we extend it to handle XCalls:

**Definition 12 (Transition function**  $\delta_x$ ) The transition  $\delta_x$  tt pt enough-heap c x xpt extends  $\delta$  to handle XCalls on state extension x, according to the extended procedure table xpt. We execute n steps by  $\delta_x^n$ .

A final configuration is reached when the program rest is SKIP. In this case the transition function is the identity. We define a relational view of the transition function that really stops in this configuration by a single introduction rule:

## Definition 13 (Transition relation)

```

\frac{c.\mathsf{prog} \neq \mathsf{SKIP}}{tt,\!pt,\!enough\!-\!heap,\!xpt\!\vdash_{\mathsf{ss}} |(c,\,x)| \rightarrow \delta_{\mathsf{x}}\ tt\ pt\ enough\!-\!heap\ c\ x\ xpt}

```

We refer to the reflexive transitive closure by substituting the arrow  $\rightarrow$  by  $\rightarrow^*$ .

As the symbol tables of the memories store typing information we do not need further components to describe well-typed configurations.

**Definition 14 (Valid configurations)** A configuration c is in set valid-COSS tt pt valid<sub>asm</sub> xpt if basic well-formedness and typing constraints hold, in particular:

- unique identifiers (cf. Definition 10),

- procedure bodies are well-typed and contain a single return statement at the end,

- the predicate  $valid_{\sf asm}$  holds for all instructions in inline assembly statements, i.e., these instructions are well-typed,

- all memory frames are well-typed and contain only valid pointers, i.e., pointers which point to existing g-variables,

- the program rest conforms with the procedure table, i.e., all statements in the program rest are from one of the procedures and their order follows certain rules (cf. [Lei08, Section 5.4]), and

- the number of return statements in the program rest is strictly smaller than the number of stack frames.

### 3.4 Property transfer

Because the level of detail increases towards the lower layers, typically the amount of invariants on the configurations increases. For example take procedure calls. In the small-step semantics we explicitly maintain a frame stack. In a valid configuration there are at least as many frames on the stack as there are open return statements in the program rest. Already in the big-step semantics there is no need for a frame stack, because it abstracts the whole procedure call to one single step in the execution. In the light of property transfer the invariants of lower layers can be divided into two categories: (i) constraints necessary to establish the abstraction and to justify the property transfer and (ii) additional invariants only meaningful for the lower layers.

When composing results at the lower layer we have to ensure that the first category of invariants hold as a prerequisite to apply the transfer theorem. Moreover, the transferred result must maintain the second kind of invariants since those properties may be needed for further reasoning at the lower layer. For example consider reasoning about a procedure call on the small-step semantics. We are in a valid configuration with a certain frame stack and attempt to use a functional property of the procedure that we have proven using Hoare logics. Since the transfer theorem only works for welltyped configurations we have to know that in our current configuration the program is well-typed and that the memory also respects this typing. If also the precondition of the Hoare triple holds we can apply the property transfer theorem and derive that the postcondition holds for the final state of the procedure call. The postcondition itself only refers to the topmost frame, since the frame stack is no longer visible in the Hoare logic. Additionally, we want to ensure that the final configuration is still well-typed (type safety) and that the procedure call has only affected the topmost frame, so that properties on the lower frames still hold. These additional invariants appear in the following transfer theorems to preserve state information used for seamless integration and reasoning at the lower level.

The granularity on which we transfer Hoare triples down to the small-step semantics is procedure calls. As the transfer theorems employ constraints on the procedures, we have to be careful not to become too restrictive. Especially the step from the Hoare logic layer to the big-step semantics is critical since we switch from a shallow to a deep embedding of the state space. It would make no sense to define abstractions and prove properties about procedures, variables and types that are not subject of the transfer.

The transfer theorems are defined relative to the *program context* which consists of the type table, the procedure table, and the symbol table for global variables. At the Hoare layer we start with a minimal program context that is necessary to define the procedure we attempt to transfer. After transferring the result to the big-step layer we extend this minimal context to the target context. This way constraints on procedures only have to hold for the minimal context.

## 3.4.1 Hoare to big-step

The transfer of results from the Hoare logic level to the big-step level has one peculiarity: we switch from a shallow embedding of the state space to a deep embedding. At the big-step level all programming language values are embedded into a single data type and memory is formulated as a partial function from variable names to those values. This uniform representation is quite natural for the formulation of the language semantics. For the verification of individual programs within the Hoare logic however, every variable becomes an own field in the state space record, with its own HOL type. This unification of programming language typing with HOL typing brings the crucial benefit of automatic type inference to the Hoare logic, which relieves us from maintaining explicit typing constraints in the pre- and postconditions of Hoare triples. However, it comes at a cost that shows up when transferring results to the big-step level. As the state representation depends on the individual program we cannot generically define an abstraction function from a big-step memory configuration to a Hoare logic memory configuration. However, we can still develop a general property transfer theory by employing Isabelle's locales. We introduce abstraction functions for the core operations (lookup and update of atomic state components) as locale parameters, for which we assume commutativity properties. On the basis of these functions we can define further abstractions that allow the simulation of expression evaluation, left-expressions, assignments, and finally statements. This gives us an abstract theory of property transfer based on the assumptions of the locale. For any concrete program, where the state space in the Hoare logic is fixed, we can actually define the basic abstraction functions and discharge the assumptions of the locale by proving the commutativity properties. As the definition of these functions and the proofs are schematic we have automated the proofs with tactics.

In the course of building derived abstractions and proving properties on them more and more information about the big-step configuration has to be made available, in particular variable declarations with their type information. This information is made available via the following locale parameters: the type table tt, typing for global variables GT, local variables LT, and heap locations HT, and finally the C0 program  $\Pi$ , declared at the more detailed big-step level. The requirements on the parameters are straightforward (e.g.,  $tt = \text{tnenv } \Pi$ ) and the intuition about them is sufficient for the course of this article. A thorough treatment can be found in [Sch06].

Both the abstraction function  $abs_s$  for a C0 statement and the abstraction function  $abs_\sigma$  for a big-step state are parametrized by a procedure name pn. Thereby the abstraction functions can discriminate between local and global variables. Moreover, a big-step state can correspond to several states in the Hoare logic. The reason is that the Hoare logic does not distinguish global and local variables, they lie side by side in the same state record. A big-step state only constrains the value of the active local variables, the variables of other procedures are irrelevant and hence any valuation of them in the Hoare logic is fine. Thus the function  $abs_\sigma$  yields a set of abstract states.

The main constraints we put on the program and the big-step configurations for which we attempt to transfer Hoare triples are type constraints. Only in a well-typed C0 setting the abstraction works out, since at the level of the Hoare logic typing is already enforced by Isabelle's type inference, due to the shallow embedding.

The cornerstone of the following transfer theorem is to strengthen the precondition from the abstract  $P_h$  to the big-step variant P and similarly to weaken the post-condition from the abstract  $Q_h$  to Q. These basic steps are decorated with validity constraints and frame conditions. The Hoare triple we attempt to transfer depends on the universally quantified auxiliary variable Z. By this the pre- and postcondition can be connected with each other [Kle99]. Typically Z fixes (parts of) the pre-state such that the post state can refer to it, e.g., to express frame conditions. Note that in the last premise of the theorem the auxiliary variable Z is existentially quantified and can depend on both versions of the initial state  $\sigma_h$  and  $\sigma$ , respectively.

The program has to be valid and the set of local variables L is determined by the current procedure pn. Most of following preconditions can rely on a big-step state  $\sigma$ that satisfies the precondition. For those constraints that directly refer to  $\sigma$  the reason is obvious. For the typing constraint on the statement s the dependency on  $\sigma$  is introduced via the heap typing HT. Imagine a pointer value as parameter of a procedure call specification. From the type constraints of the procedure we can infer the type name the pointer points to, which has to coincide with the heap typing HT at the location of the pointer. This location is part of the heap which also has to conform to the heap typing HT. For definite assignment the locations we assume to be assigned must be subset of the actually assigned values in the initial state. As the statement s we transfer is usually a procedure call, the definite assignment check can already be passed by an empty set A. This makes the subsumption test  $A \subseteq \mathsf{dom}\ \sigma.\mathsf{lcls}\ \mathsf{trivial}\ \mathsf{and}\ \mathsf{also}\ \mathsf{imposes}$ no constraints on the typing of local variables since LT  $pn \upharpoonright_A$  becomes the empty map for  $A = \{\}$ . The way we construct the state abstraction ensures  $\forall \sigma$ .  $abs_{\sigma}$  pn  $\sigma \neq \{\}$ . The last premise is the promised connections between the preconditions P and  $P_h$  and the postconditions Q and  $Q_h$ . During execution of the statement s the heap may grow due to new memory allocations. Hence the heap typing for the final state HT' is an extension of the initial heap typing. Similar the statement may assign local variables which are predicted by A s, and hence the final state must respect the typing of those additionally initialized variables. The last two conjuncts of the precondition in the final implication are pure frame conditions. All global variables that are not mentioned in the global typing GT and all heap locations that are not typed according to heap typing HT and the type table  $t\bar{t}$  stay the same. These frame conditions are useful when we extend the typing environments, e.g., to embed the result in a bigger program.

## Theorem 1 (Property transfer from Hoare to big-step)

This theorem is a corollary from simulation properties between the operational semantics of Simpl and C0, which are outlined in [AHL<sup>+</sup>08] and detailed in [Sch06]. The core theorems are the correspondence of a C0 big-step execution and a Simpl execution and preservation of termination from Simpl to C0.<sup>2</sup> The simulation theorem is built from a couple of lemmas along the syntactic entities of C0: expression evaluation, left-expression evaluation, assignment, and statement execution. The latter one is proven by rule-induction on the big-step semantics, the former ones by induction on the (left-) expressions or the structure of the involved types. Most effort goes into the simulation of assignment. The reason for this are the differences in the representation of aggregate C0 values, which are broken down to their components in the split heap model of Simpl. Preservation of termination builds on the simulation theorem and is proven by induction on the termination relation. Altogether the verification effort sums up to about 0.75 person years. Some examples for applying the transfer theorems to simple procedures can be found in Section 8.8 of [Sch06].

### 3.4.2 Big-step to small-step

In addition to the standard constraints on configurations valid-COSS we impose further restrictions for the purpose of property transfer. (i) Certain statements and expressions are not allowed since they are not supported by the big-step semantics or the Hoare logics, namely Addroff, ESCALL, and inline assembly. The function scalls collects the procedure calls of a statement and the set SCalls inductively collects further calls in the procedure environment for the given initial set. (ii) The global variables have to be initialized and we only allow pointers to (root) heap locations in memory (the smallstep semantics additionally allows pointers to global variables or to subcomponents of an aggregate value). (iii) Moreover, every type in the heap has to have a proper type name in the type environment. This is attributable to a subtle deviation in the different semantic formalizations. Whereas the small-step semantics directly maps pointers to types, the big-step semantics makes an indirection via type names. (iv) The small-step semantics maintains a frame stack for procedure calls where the destination for the return value is located (the second component of a frame). In the big-step semantics we directly store the return value within the local variables. For this purpose we reserve the variable name Res, which has to be distinct from other local and global variable names. Only root positions of local and global variables are valid return destinations. In case the return destination is a local variable it has to be defined in the frame stack below, formalized by the predicate valid-retvars. (v) Each procedure in the procedure environment has to pass the definite assignment check, where we assume parameters, local variables, and variable Res to be local, and the parameters to be initialized.<sup>4</sup> (vi) Similarly, the program rest has to pass the definite assignment check. However, as the program rest gets expanded during the small-step computation it may contain multiple returns and hence the program rest is split into several regions that correspond to procedure invocations on the frame stack. This generalization is formalized by  $\mathcal{D}$ s and LAs.

$<sup>^2\,</sup>$  Guaranteed termination form an initial configuration is formalized on top of the big-step semantics as an inductive definition.

<sup>&</sup>lt;sup>3</sup> This can be liberated by only enforcing it for the pointers to known types, such that one can allow all kind of pointers to new types when embedding the result into a bigger context.

<sup>&</sup>lt;sup>4</sup> We could liberate this by only enforcing it for the procedures in SCalls pt (scalls c.prog).

## Definition 15 (Valid small-step configurations for property transfer)

```

\begin{array}{l} \text{valid-cfg}_{\text{SS}} \ tt \ pt \ xpt \ valid_{\text{asm}} \ c \ x \equiv c \in \text{valid-COSS} \ tt \ pt \ valid_{\text{asm}} \ xpt \ \land \\ \text{noAddrOf-Asm-ESCall} \ c.\text{prog} \ \land \\ (\forall p \in \text{SCalls} \ pt \ (\text{scalls} \ c.\text{prog}). \ \text{noAddrOf-Asm-ESCall} \ (\text{the (map-of} \ pt \ p)).\text{proc-body}) \ \land \\ \text{globals-initialized} \ c.\text{mem.gm} \ \land \text{only-heap-pointer} \ c.\text{mem} \ \land \text{named-types} \ tt \ (\text{hm-st} \ c.\text{mem}) \ \land \\ \text{Res} \notin \text{fst} \ \text{'set} \ c.\text{mem.lm} \ \land \\ \text{Res} \notin \text{fst} \ \text{'set} \ c.\text{mem.lm} \ \land \\ (\forall gv \in \text{snd} \ \text{'set} \ c.\text{mem.lm. is-root-gvar} \ gv) \ \land \\ \text{valid-retvars} \ (\text{snd} \ (\text{hd} \ c.\text{mem.lm})) \ (\text{tl} \ c.\text{mem.lm}) \ \land \\ (\forall p \in \text{snd} \ \text{'set} \ pt. \\ \text{let} \ pns = \text{map} \ \text{fst} \ p.\text{proc-parameters}; \ lns = \text{map} \ \text{fst} \ p.\text{proc-local-vars} \\ \text{in} \ \mathcal{D} \ p.\text{proc-body} \ (\text{set} \ (pns \ @ \ [\text{Res}])) \ (\text{set} \ pns) \ \land \ \text{Res} \notin \text{set} \ pns \ \cup \ \text{set} \ lns) \ \land \\ \mathcal{D} \text{s} \ c.\text{prog} \ ((\text{vnames} \ c, \ \text{init-vnames} \ c) \ \cdot \text{LAs} \ (\text{snd} \ (\text{hd} \ c.\text{mem.lm})) \ (\text{tl} \ c.\text{mem.lm})) \end{array}

```

Our notion of a Hoare triple at the level of the small-step semantics is biased towards property transfer from the big-step level. We encode validity of configurations and transition invariants right into this notion and also carry some leftovers of the big-step configurations around, namely the set of local variables L and the program  $\Pi$ . The reason for this peculiarity is that the set of local variables and even the program declarations are directly encoded into each configuration in the small-step semantics. Hence we cannot relate those entities between the big- and the small-step semantics without referring to a small-step configuration which is only accessible within the preand postconditions of the Hoare triple.

We consider an initial configuration (c, x). The memory of the configuration and the extended state fulfill the precondition. Moreover the initial configuration is valid, the program rest corresponds to statement s which does not contain a return statement. As we typically transfer a single procedure call this is trivially the case. The abstraction relations between the small-step configuration and the set of local variables L, as well as the program  $\Pi$  hold. Since we define total correctness non-terminating computations are ruled out, which is denoted by the precondition  $\neg tt,pt,enough-heap,xpt \vdash_{ss} \lfloor (c,x) \rfloor \rightarrow \ldots(\infty)$ . For every computation the final configuration cx', must not be the error configuration, the postcondition has to hold, and it has to be valid. Moreover, the transition invariant between initial and final configuration has to be satisfied.

## Definition 16 (Total correctness on small-step semantics)

```

\begin{array}{l} tt,pt, enough-heap, xpt, valid_{\mathsf{asm}}, L,\Pi \models_{\mathsf{ss}} P \ s \ Q \equiv \\ \forall \ c \ x. \ (c.\mathsf{mem}, \ x) \in P \land \mathsf{valid}\text{-}\mathsf{cfg}_{\mathsf{ss}} \ tt \ pt \ xpt \ valid_{\mathsf{asm}} \ c \ x \land c.\mathsf{prog} = s \land \\ \mathsf{nr}\text{-}\mathsf{returns} \ s = 0 \land L = \{\mathsf{Res}\} \cup \mathsf{fst} \ `\mathsf{set} \ (\mathsf{toplm}\text{-}\mathsf{st} \ c.\mathsf{mem}) \land \\ \mathsf{absProg} \ tt \ pt \ (\mathsf{gm}\text{-}\mathsf{st} \ c.\mathsf{mem}) \ \Pi \longrightarrow \neg \ tt, pt, enough-heap, xpt \vdash_{\mathsf{ss}} \lfloor (c, x) \rfloor \rightarrow \ldots (\infty) \land \\ (\forall \ cx'. \ tt, pt, enough-heap, xpt \vdash_{\mathsf{ss}} \lfloor (c, x) \rfloor \rightarrow^* \ cx' \land \mathsf{final} \ cx' \longrightarrow \\ (\exists \ c' \ x' \ xs. \ cx' = \lfloor (c', x') \rfloor \land (c'.\mathsf{mem}, \ x') \in Q \land \\ \mathsf{valid}\text{-}\mathsf{cfg}_{\mathsf{ss}} \ tt \ pt \ xpt \ valid_{\mathsf{asm}} \ c' \ x' \land \\ \mathsf{transition-invariant} \ tt \ pt \ xpt \ valid_{\mathsf{asm}} \ s \ xs \ c \ x \ c' \ x')) \end{array}

```

The transition invariant captures essential invariants of the small-step computation that hold between the initial and final configuration of the procedure call that we transfer. First of all the computation only affects the topmost frame of local variables. Moreover, neither the type information of this frame nor of the global variables is changed. The type information for the heap memory may only grow. The second component of a frame stores the left-value of the return variable. This is also not modified by the current procedure call. Finally the increasing set of initialized local variables is approximated by the definite assignment analysis  $\mathcal{A}$ . In particular this ensures that the result variable of the procedure call is initialized in the final configuration.

## Definition 17 (Transition invariant)

```

transition-invariant tt pt xpt valid_{\mathsf{asm}} s xs c x c' x' \equiv \mathsf{tl} c'.\mathsf{mem.Im} = \mathsf{tl} c.\mathsf{mem.Im} \land \mathsf{topIm-st} c'.\mathsf{mem} = \mathsf{topIm-st} c.\mathsf{mem} \land \mathsf{gm-st} c'.\mathsf{mem} = \mathsf{gm-st} c.\mathsf{mem} \land \mathsf{hm-st} c'.\mathsf{mem} = \mathsf{hm-st} c.\mathsf{mem} @ xs \land \mathsf{snd} (\mathsf{hd} c'.\mathsf{mem.Im}) = \mathsf{snd} (\mathsf{hd} c.\mathsf{mem.Im}) \land (\mathsf{fst} (\mathsf{hd} c.\mathsf{mem.Im})).init-vars <math>\cup vnames c \cap \mathcal{A} s \subseteq (\mathsf{fst} (\mathsf{hd} c'.\mathsf{mem.Im})).init-vars

```

At its core the single premise of the following transfer theorem is a variant of an adaption theorem in Hoare logics. We strengthen the precondition and weaken the postcondition. Additionally, we take the different layers and the system invariants of the small-step layer into account. For an arbitrary initial configuration that fulfills the constraints of small-step validity and the precondition P we have to supply a big-step Hoare triple  $\Pi$ ,sz, $L\models_{bs}P_{bs}$  s  $Q_{bs}$  such that the big-step abstraction of the configuration fulfills the precondition  $P_{bs}$ . For a final valid small-step configuration, that fulfills the transition invariant and for which the big-step abstraction fulfills the postcondition  $Q_{bs}$  we have to derive the small-step postcondition  $Q_{configuration}$ . Note the existential quantification on the big-step pre- and postcondition. It is under the universal quantification of the initial configuration and hence can depend on this configuration. The function absState is used to abstract a small-step configuration to a big-step state.

## Theorem 2 (Property transfer from big-step to small-step)

```

\begin{array}{l} \forall \textit{c} \textit{x}. \; \text{valid-cfg}_{\text{ss}} \; \textit{tt} \; \textit{pt} \; \textit{valid}_{\text{asm}} \; \textit{c} \; \textit{x} \; \land \; \textit{c}. \text{prog} = s \; \land \; \text{nr-returns} \; s = 0 \; \land \; (\textit{c}. \text{mem}, \textit{x}) \in P \; \land \\ L = \{\text{Res}\} \; \cup \; \text{fst} \; \text{`set} \; (\text{topIm-st} \; \textit{c}. \text{mem}) \; \land \; \text{absProg} \; \textit{tt} \; \textit{pt} \; (\text{gm-st} \; \textit{c}. \text{mem}) \; \varPi \; \longrightarrow \\ (\exists P_{\text{bs}} \; Q_{\text{bs}}. \; \varPi, \textit{sz}, L \models_{\text{bs}} P_{\text{bs}} \; s \; Q_{\text{bs}} \; \land \; \text{absState} \; \textit{hs} \; \textit{sz} \; \textit{c}. \text{mem} \; \textit{x} \in P_{\text{bs}} \; \land \\ (\forall \textit{c'} \; \textit{x'} \; \textit{xs}. \\ \text{valid-cfg}_{\text{ss}} \; \textit{tt} \; \textit{pt} \; \textit{valid}_{\text{asm}} \; \textit{c'} \; \textit{x'} \; \land \\ \text{transition-invariant} \; \textit{tt} \; \textit{pt} \; \textit{valid}_{\text{asm}} \; \textit{s} \; \textit{xs} \; \textit{c} \; \textit{x} \; \textit{c'} \; \textit{x'} \; \land \\ \text{absState} \; \textit{hs} \; \textit{sz} \; \textit{c'}. \text{mem} \; \textit{x'} \in Q_{\text{bs}} \; \longrightarrow \; (\textit{c'}. \text{mem}, \; \textit{x'}) \in Q)) \\ \Longrightarrow \textit{tt,pt,enough-heap,xpt,valid}_{\text{asm}} L, \varPi \models_{\text{ss}} P \; \textit{s} \; Q \\ \end{array}

```

As for the transfer from Simpl to the C0 big-step semantics, the above theorem is a corollary from simulation properties between the big-step and the small-step semantics. To separate data-refinement arguments from computation steps, we introduce an intermediate small-step semantics [AHL<sup>+</sup>08] that on the one hand shares the state space with the big-step semantics and on the other and has the same granularity of computation as the small-step semantics. We first prove that termination in the big-step semantics implies a terminating computation in the intermediate small-step semantics and that a terminating computation in the intermediate semantics has a corresponding execution in the big-step semantics. The second half is to prove that every computation step in the small-step semantics has a corresponding step in the intermediate semantics. Analogous to the simulation proofs behind Theorem 1 we build our lemmas along the syntactic entities of C0. As before the simulation of the assignment was the most time-consuming task, for similar reasons: the transition from aggregate values on the big-step level to flat values on the small-step level. The simulation between the big-step semantics and the intermediate semantics accounted to two weeks of work, whereas the second half from the intermediate semantics to the small-step semantics consumed almost one person year. The reason is both due to some technically involved arguments and intermediate notions, especially regarding the assignment, but also due to some minor deviations in the formalizations of corresponding aspects in the various semantics, which were developed at different sites. Some were adjusted and others were just bridged, because an accommodation of existing theories built on top of the semantics would have been too expensive.

Reasoning about heap consumption. In Theorem 2 we have hidden a precondition, which relates the enough heap predicate enough-heap and the size function sz:

```

\neg \ enough\text{-}heap \ m \ T \Longrightarrow \mathsf{free}\text{-}\mathsf{heap}\text{-}\mathsf{size} \ hs \ sz \ (\mathsf{hm}\text{-}\mathsf{st} \ m) < sz \ T

```

If according to enough-heap insufficient heap memory is available to allocate an object of type T in memory m, then this is consistent with the size function sz. The auxiliary function free-heap-size subtracts all the sizes of the type entries in the symbol table of the heap from the initial heap size hs. Note that we do not demand anything for the case that enough-heap is successful. The reason is that in the big-step semantics and the Hoare logic we treat memory allocation 'semi'-nondeterministically: if enough memory is left allocation always succeeds and returns a new pointer, otherwise it nondeterministically returns a new pointer or the null pointer. The motivation is the integration of garbage collection into the picture. In this scenario the Hoare logic only has an approximate knowledge about the free heap, since it just maintains a counter that is decremented by the size of the type for the freshly allocated object. The Hoare logic cannot compute heap consumption exactly because it only sees the current stack frame and, thus, does not know the set of reachable heap objects. So in case insufficient memory is predicted, this might not be the case in the implementation, since a garbage collector could have made more heap available in the meantime. This can be captured in a garbage collector aware enough-heap predicate.

Employing Hoare triples in redex position. At this point we are able to transfer a Hoare triple for a single procedure call to the small-step level. However, we typically attempt to integrate this procedure call into a bigger computation and hence the program rest in an intermediate configuration is not just this single procedure call, but rather the procedure call is at the redex position in the program rest. The following theorem allows us to employ the Hoare triple in such a configuration.

## Theorem 3 (Employ Hoare triple in redex position)

Note the subtle change in validity of a configuration. Whereas valid-cfg<sub>ss</sub> demands that the whole program rest does not contain assembly, address-of or external calls (cf. Definition 15), valid-cfg<sub>ss</sub> 'drops this restriction. We ensure in the precondition that it holds for the redex though. One basic motivation of reasoning at the low abstraction level of the small-step semantics instead of the convenient Hoare logic level is the ability to combine ordinary C0-computation with inline assembly code. Hence, it would be worthless if we were incapable of using the transferred result in a situation where inline assembly code is part of the program rest. We start in a configuration where the redex of the program rest agrees with the statement in the Hoare triple. As we have total correctness we know that the computation leads to a state where the statement is completely executed, i.e., has evaluated to SKIP. The program rest of

$<sup>^{5}</sup>$  Note that the small-step semantics is deterministic. Hence, restricting ourselves to one particular final configuration via the existential quantification is sufficient.

this configuration is obtained by substituting the redex position of the initial program rest with SKIP. In the remainder of the theorem the usual properties about the initial and final configuration show up. The main argument in the proof is a straightforward consequence from the transition function extending the computation by unfolding the program rest in the redex position.

### 4 VAMP

The VAMP architecture is based on the DLX architecture [HP96] and was initially presented in [MP00]. An implementation of the VAMP has been formally verified in 2003 [BJK $^+$ 03, BJK $^+$ 06]. Since then, the VAMP has been extended with address translation and support for I/O devices [DHP05, AHK $^+$ 07, TS08].

There are three models related to the VAMP architecture; from concrete to abstract ones these are the VAMP's gate-level implementation, its instruction set architecture (ISA) specification, and its assembly language specification. For each model, one variant with device support and one variant without device support is defined. Simulation proofs relate two models of adjacent layers.

In this section we sketch the definitions of the models above the gate level and the relevant simulation results. Details on the gate-level implementation of the VAMP and its verification can be found elsewhere [TS08].

### 4.1 Assembly

The VAMP assembly language specification is intended to be a convenient layer for implementation and verification of low-level applications. Thus, it abstracts from certain aspects of lower layers which are irrelevant for most applications.

In the VAMP assembly machine, data is represented as integers while addresses are represented as naturals. This representation is optimized for applications working with integers; arguments regarding naturals and bit vector operations requires the use of conversion functions from / to integers. For example, the two functions to-nat32 and to-int32 convert between 32-bit integers and naturals.

A VAMP assembly configuration asm is a record with the following components: two program counters asm.dpc and asm.pcp for implementing the delayed branch mechanism, which hold the addresses of the current and next instruction, the general-purpose and special-purpose register files asm.gprs and asm.sprs, which are both lists of data, and the main memory asm.mm, which is a map from addresses to data. With m[a, d] we obtain from memory m the content of length d starting at address a.

**Definition 18 (Valid assembly configuration)** A VAMP assembly configuration is called valid, denoted by the predicate valid-asm, if it fulfills certain basic well-formedness conditions: the program counters must be 32-bit naturals, register files must contain 32 registers, and all registers and memory cells must be 32-bit integers.

Instructions are represented with an abstract data type and converted between memory cells with conversion functions, e.g., with the function to-instr on instruction fetch. Thus, the function current-instr  $asm \equiv \text{to-instr} \ (asm.mm \ (asm.dpc \ div \ 4))$  denotes the instruction that will be executed next in the assembly machine. A VAMP

assembly instruction is said to be valid if its register names and immediate constants are in the correct range. We denote this fact by the predicate is-instr.

The VAMP assembly transition function  $\delta_{\mathsf{asm}}$  computes for a given assembly configuration asm the next configuration asm'. The transition is specified by a simple case distinction over current-instr asm. We use the notation  $\delta_{\mathsf{asm}}^n$  asm to denote n steps of the assembly machine starting in configuration asm.

**Definition 19 (Legal instructions)** The assembly machine does not model execution of all instruction of the underlying ISA (cf. next section). Interrupt related instructions (RFE and TRAP) are handled by dummy transitions and we assume that they do not occur in the programs executed by the assembly machine (cf. Section 4.4). Access to special purpose registers is only supported in system mode. We formalize these restrictions with the predicate legal-asm-instr which is false for RFE and for instructions accessing a special purpose register in user mode.

#### 4.2 Instruction set architecture

The VAMP instruction set architecture (ISA) serves as a specification of the VAMP gate-level hardware. There are three key differences of the VAMP ISA with respect to the more abstract VAMP assembly language: the VAMP ISA supports execution modes, address translation, and interrupt handling.

In system mode, programs can directly access the memory and fully control the architecture via a number of privileged instructions. In user mode, memory accesses are subject to address translation and attempts to execute a privileged instruction will result in an exception. The architecture responds to such exceptions, page-faults, and other interrupts by entering system mode and continuing execution at address 0, the start of the interrupt service routine (ISR). Normally, user mode is re-entered, continuing execution at the interrupted location, by issuing the privileged instruction RFE, which marks the end of the ISR.

Another, rather technical difference of the VAMP ISA is that some parts of its configuration and operation are defined in terms of bit vectors rather than naturals and integers, which is closer to the actual hardware implementation.

By design of the VAMP assembly model, no general simulation theorem can be established with respect to the VAMP ISA. However, equivalence can be established for system mode computations in which no interrupts occur, cf. Section 4.4. Similarly, when user mode computation is *virtualized* by the system software an equivalence result can also be established; this is an important part of the correctness of our CVM model discussed later in this article (cf. Section 6).

A configuration isa of the VAMP instruction set architecture is a record, which has the same components than a VAMP assembly configuration has, although differently typed: the program counters isa.dpc and isa.pcp are bit vectors, the general-purpose and special-purpose registers isa.gprs and isa.sprs are functions from bit vectors to bit vectors, the main memory isa.mm is a function from bit vectors to pairs of bit vectors. Although bit vectors can have variable length in Isabelle, all bit vectors in the VAMP ISA have constant length, which is an invariant preserved during computation: register addresses are 5-bit bit vectors, register values are 32-bit bit vectors, which we also call words, and the main memory maps 29-bit double-word addresses to pairs of words.

<sup>&</sup>lt;sup>6</sup> Older VAMP versions had floating-point registers and units [BJK<sup>+</sup>03], not needed here.

Transition function. The transition function of the VAMP instruction set architecture is denoted  $\delta_{isa}$  is a eev mifo. It takes a current configuration is a, a bit vector of external interrupts (including a reset line), and a device output mifo as inputs. The latter two parameters mostly make sense if the VAMP is connected to devices (as sketched below). The transition function returns an updated configuration asm'.

Address translation. The VAMP provides a single-level address translation mechanism, which our CVM implementation uses to virtualize user process execution (cf. Sections 6 ff.). We sketch the relevant definitions of functions based on natural numbers, which is the form in which we will use them later.

VAMP's main memory is organized in pages, which are aligned chunks of data of size  $2^{12}$  bytes. Two special purpose registers are relevant to address translation: The page table origin register PTO and the page table length register PTL designate a special region in main memory called page table consisting of word-sized page-table entries (PTEs). The page index px  $va \equiv va$  div  $2^{12}$  of a virtual address va is used as an index into this table. If  $va > \mathsf{PTL}$  a page-fault exception is generated. Otherwise let pte denote the page table entry with index px va. It consists of three components: (i) the physical-page index ppx = pte div  $2^{12}$ , (ii) the valid bit v = pte div  $2^{11}$  mod 2, and (iii) the protection bit p = pte div  $2^{10}$  mod 2. If the valid bit is on, read accesses to the virtual address are allowed. If additionally the protection bit is cleared, also writes are allowed. If these conditions are met, an access to a virtual address va will be performed on the physical address  $ppx * 2^{12} + va$  mod  $2^{12}$ .

#### 4.3 Devices and their integration

Devices. We model devices as deterministic finite-state machines communicating with an external environment and the processor. The external environment is used to model non-determinism and communication; a network interface card, for example, sends and receives network packets. The processor accesses a device by reading or writing special addresses. The devices, in turn, can signal interrupts to the processor; Direct memory access (DMA) is not considered.

Formally, the interface between the processor and devices is defined by memory interface inputs mifi and outputs mifo, which encode the processor's request and the device's response to the request. A device of type x is represented by (i) types for its external input, external output, and configuration, (ii) a predicate  $intr_x$  on its configuration that indicates pending interrupts, and (iii) a transition function  $\delta_x$ , which takes an input from the external environment, an input from the processor, and a device configuration as parameters and returns an updated configuration, an output to the processor, and an output to the external environment.

To generalize over different device types (hard disk, network card, etc.) we define a generalized external environment and device configurations as abstract data types. The transition function  $\delta_{dev}$  eifi mifi d=(d', mifo, eifo) can be used for multiple device types. Likewise, the predicate intr d indicates pending interrupts.

For the definition of non-interference predicates (and also for block operations, which are not needed here) we also need a transition functions  $\delta_{\mathsf{dev}}^*$  eifis mifis d for many device steps, which consumes a list of memory and externals inputs.

Models with devices. At the gate-level hardware, up to eight devices operate in lockstep with the processor, running with the same clock. However, moving to the instruction set architecture and to assembly, we lose granularity and hence timing information. We compensate for this loss by introducing interleaved execution of devices and the processor. An oracle, called execution sequence, determines when some device or the processor takes a step.

**Definition 20 (Execution sequence)** An execution sequence element is equal to  $\bot$  if at a certain point the processor takes a step or equal to  $\lfloor (DID, eifi) \rfloor$  if the device with identifier DID and external input eifi takes a step. An execution sequence  $seq_{asm}$  is a map from natural numbers to execution sequence elements.

First, we define the model VAMP assembly with devices.

Definition 21 (Configuration of VAMP assembly with devices) A configuration  $asm_D$  of the VAMP assembly with devices model is a record with two fields:  $asm_D.proc$ , the assembly state of the processor and  $asm_D.devs$ , a map from device identifiers to device configurations.

Definition 22 (Transitions of VAMP assembly with devices) Given the execution sequence  $seq_{asm}$ , the current VAMP assembly with devices state  $asm_D$  and the number N, the transition  $\Delta_{asm}^N$   $seq_{asm}$   $asm_D$  returns the state reached after the execution of N steps of the sequence  $seq_{asm}$ .

Second, we define the model VAMP ISA with devices.

**Definition 23 (Configuration of VAMP ISA with devices)** A configuration  $isa_D$  of the model VAMP ISA with devices is a record with two fields:  $isa_D.proc$ , the ISA state of the processor and  $isa_D.devs$ , a map from device identifiers to device configurations.

In the transition function of the VAMP ISA with devices the previously defined execution sequence is split into two separate functions,  $seq_{isa}$  and eifis. This is closer to the gate-level implementation and eases the correctness proof for the hardware. The first function determines for step N whether the processor or one of the devices is executing, the second function maps step numbers to inputs from the external environment. To convert both functions into a VAMP assembly execution sequence, we define the conversion function to-seq<sub>asm</sub>  $seq_{isa}$  eifis  $N = \bot$  iff  $seq_{isa}$   $N = \bot$ , and to-seq<sub>asm</sub>  $seq_{isa}$  eifis  $N = \lfloor DID \rfloor$  and eifis N = eifi.